#### PULP within the Open Source Hardware Landscape

Integrated Systems Laboratory (ETH Zürich)

Frank K. Gürkaynak kgf@iis.ee.ethz.ch

**PULP Platform** Open Source Hardware, the way it should be!

@pulp\_platform >> pulp-platform.org

youtube.com/pulp\_platform

## Parallel Ultra Low Power (PULP) Platform

Research on open-source energy-efficient computing

#### We have designed and tested more than 50 PULP ICs 2014 2015 2016 2017 2018 2019 2020 2021 2013 2022 (3) (5) (3) (2) (6) (7) (3) (7) (9) (10)PULPv1 Fulmine VivoSoC 2.001 Mr. Wolf Baikonur Kraken Diana Dustin Occamy Poseidon STM 28FDSOI UMC 65 UMC 65 **SMIC 130** TSMC 40 GF 22FDX TSMC 65 GF 22FDX GF 12LPP GF 22FDX Dual 64bit RISC-V IoT processor Multi-core 4-core system 4-core system Mixed signal 8+1 core IoT IoT processor ML accelerator 64bit RISC-V with with ML and core. 3x 8core with Spiking with 216 + 1 system for with 16 cores processor processor core. 32bit snitch clusters, Neural and Crypto biosignal and QNN cores and HBM approximate Microcontroller interface FPUs accelerators acquisiton Body biasing test enhancements Ternary system, ML Inference vehicle rator Engines

#### Check http://asic.ethz.ch for all our chips

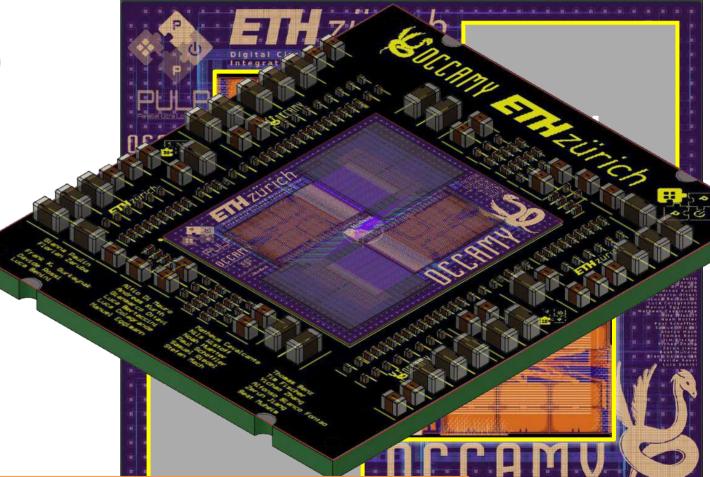

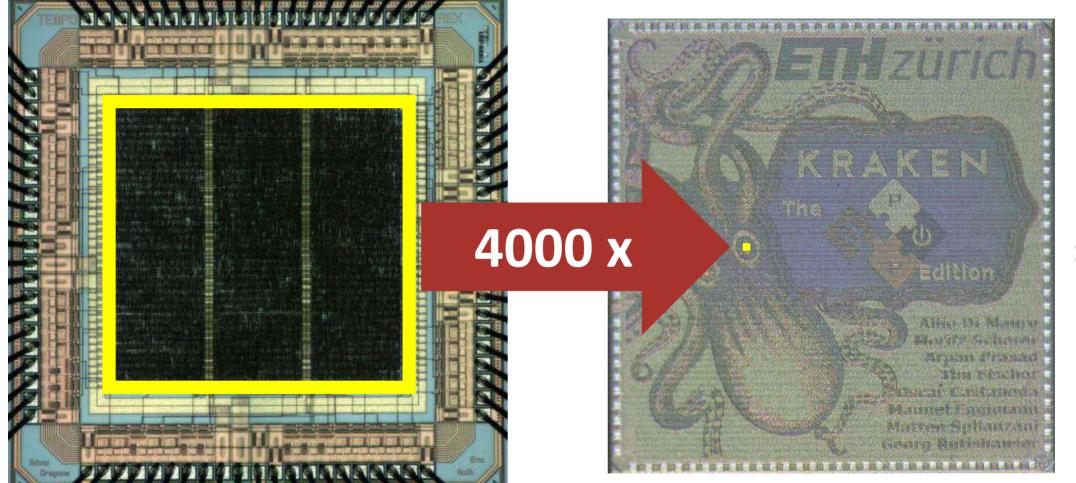

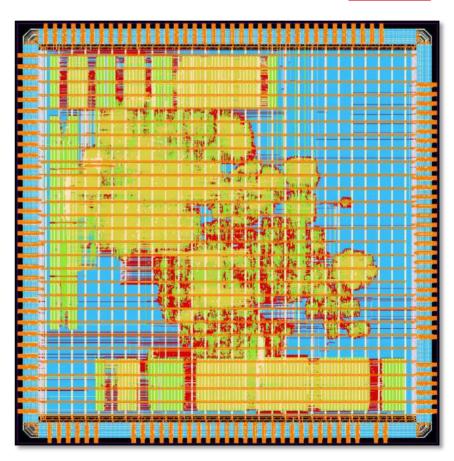

# Including some very complex designs like Occamy

- Chiplet based design

- 2x Compute chiplets (Occamy)

- 216+1 RISC-V cores

- 0.75 TFLOP/s for the system

- GF12LPP

- Running at 1 GHz

- 2x 16GB HBM DRAMs

- Silicon Interposer

- GF 65nm 26mm x 23mm

- Waiting for assembly to finish

More on Occamy – https://pulp-platform.org/occamy/

# All of our designs are open source hardware

- All our development is on GitHub using a permissive license

- HDL source code, testbenches, software development kit, virtual platform

#### https://github.com/pulp-platform

• Allows anyone to use, change, and make products without restrictions.

ALMA MATER STUDIORUM

**ETH** zürich

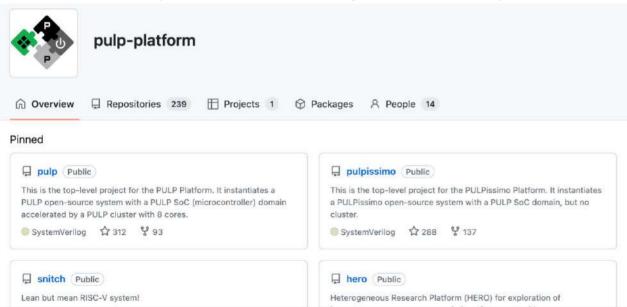

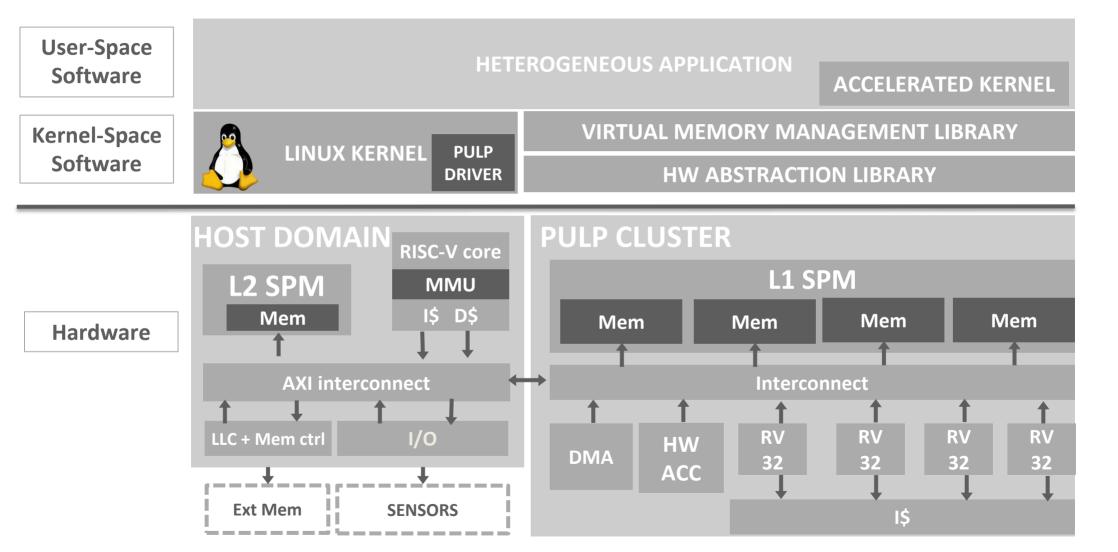

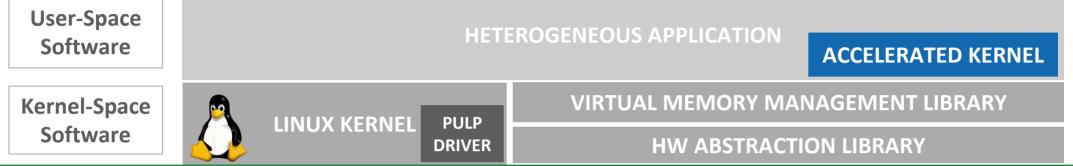

#### Heterogeneous Research Platform (HERO)

HERO is an **FPGA-based research platform** that enables accurate and fast exploration of heterogeneous computers consisting of programmable many-core accelerators and an application-class host CPU. Currently, 32-bit RISC-V cores are supported in the accelerator and 64-bit ARMv8 or RISC-V cores as host CPU. HERO allows to seamlessly share data between host and accelerator through a unified heterogeneous programming interface based on OpenMP 4.5 and a mixed-data-model, mixed-ISA heterogeneous compiler based on LLVM.

HERO's hardware architecture, shown below, combines a general-purpose host CPU (in the upper left corner) with a domain-specific programmable many-core accelerator (on the right side) so that data in the main memory (in the lower left corner) can be shared effectively.

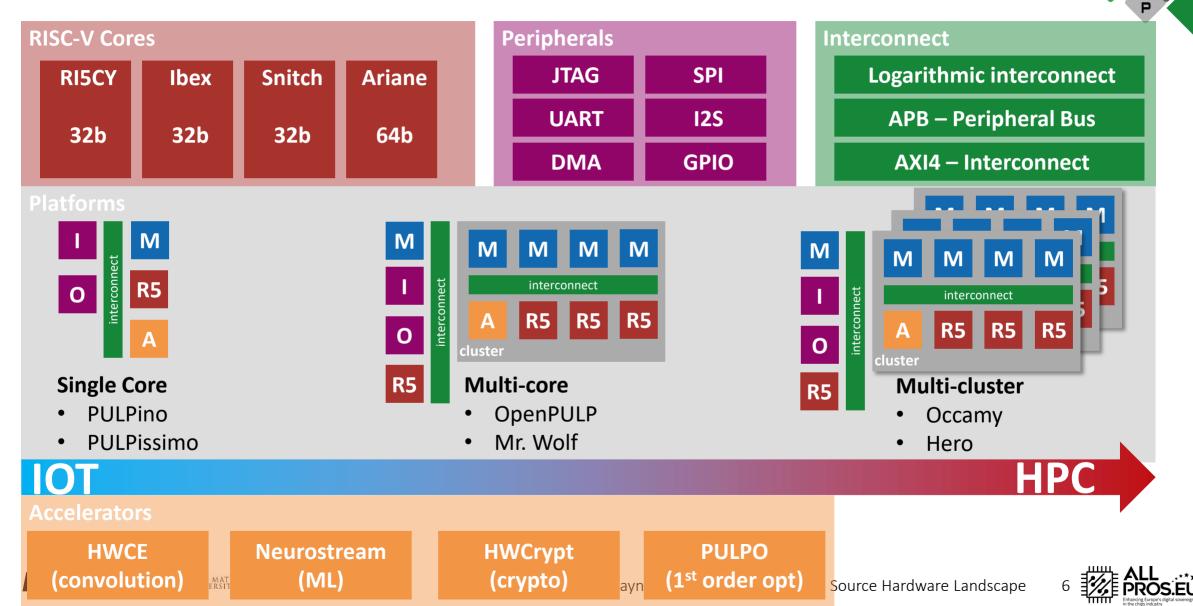

## What PULP provides is a box of building blocks

#### How does PULP collaborate with 3<sup>rd</sup> parties?

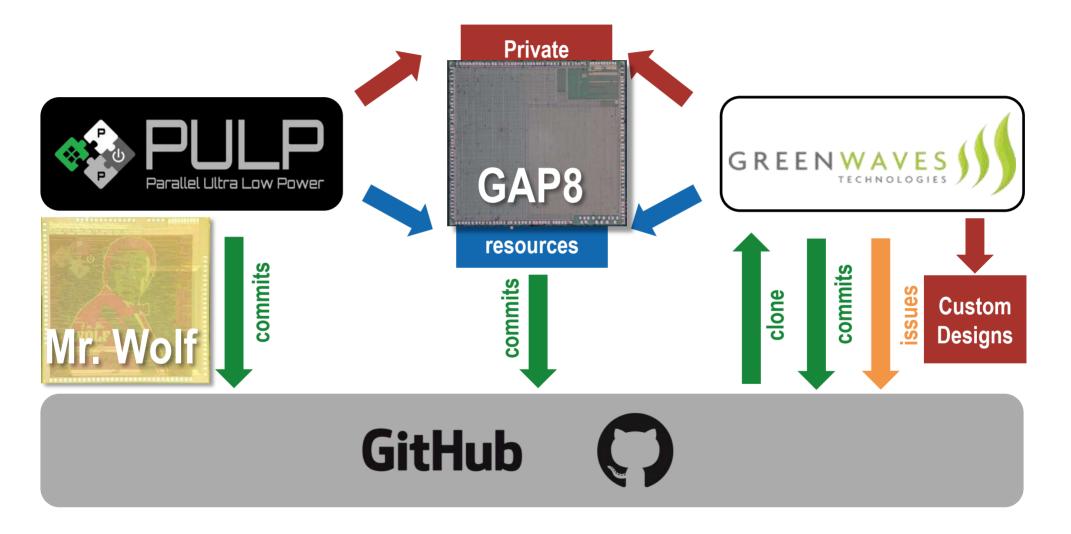

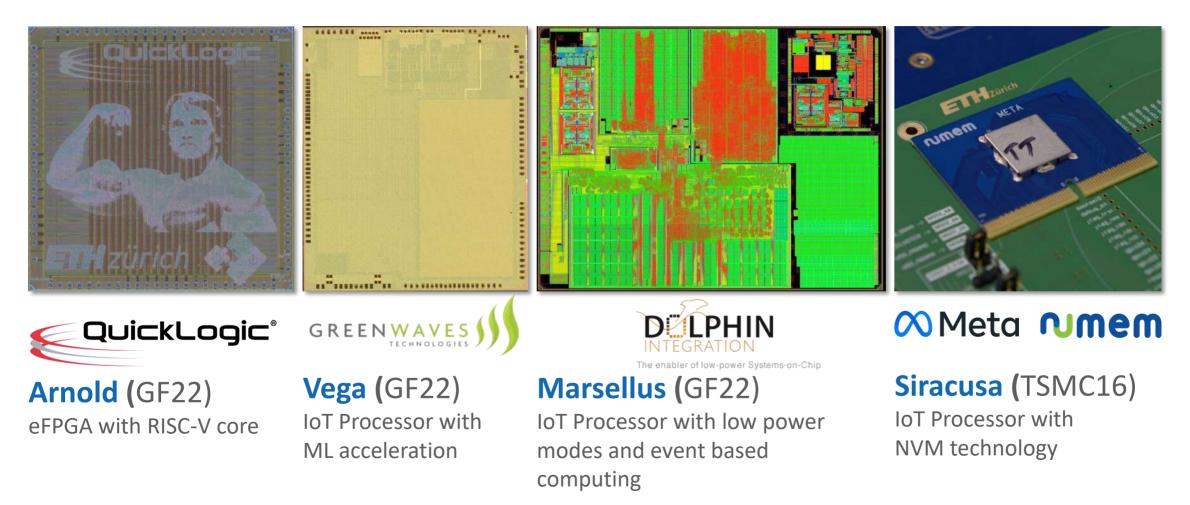

# The open model led to successful industry collaborations

**ETH** zürich

ALMA MATER STUDIORUM

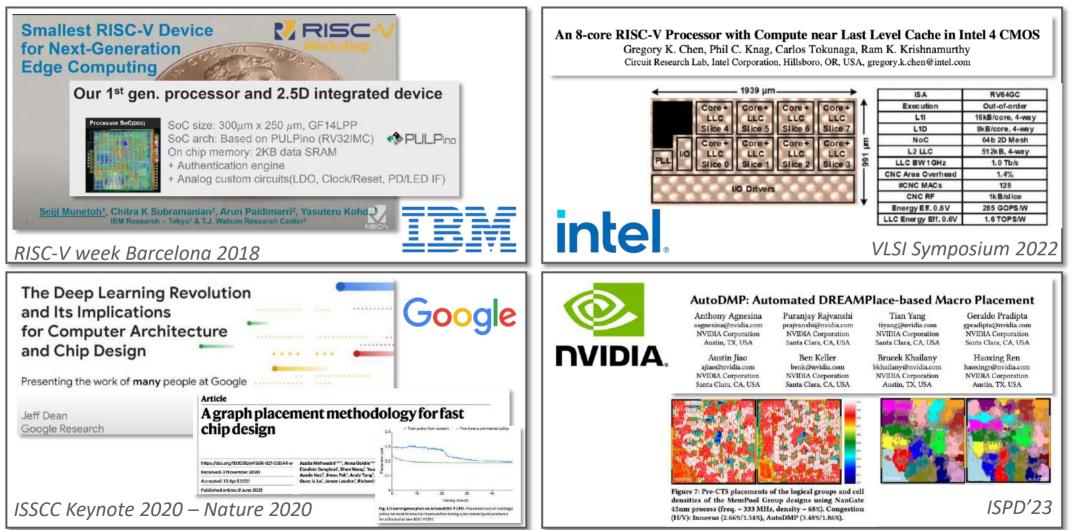

### And many have used our work for their research

**ETH** zürich

ALMA MATER STUDIORUM

Frank K. Gürkaynak - PULP within the Open Source Hardware Landscape

#### In the last 20 years IC Design has changed a lot

What used to be a complete chip is now a small part of a SoC !

80 MGE

e Landscape

3.3 mm

## There is so much that makes up a modern SoC

# In a typical design, innovation is only in a limited scope

#### **Open-source silicon-proven SoC template helps concentrate work where it counts**

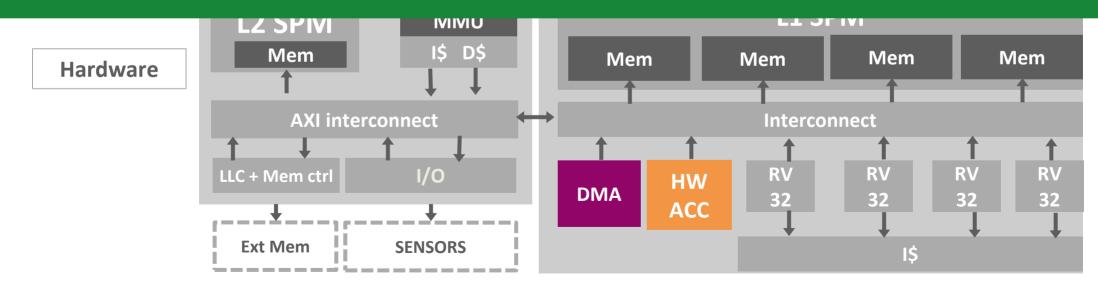

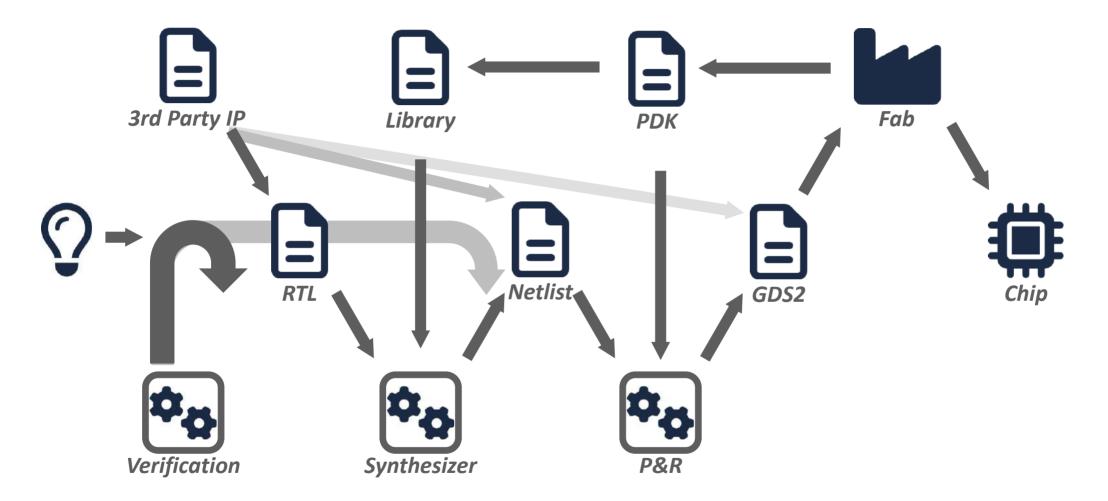

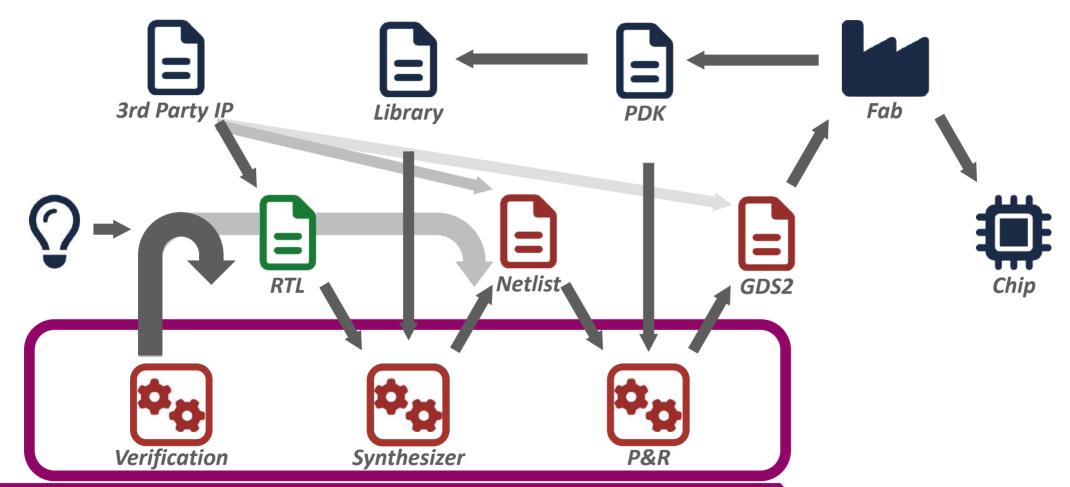

#### Simplified IC design flow

# Simplified IC design flow: at the moment only RTL

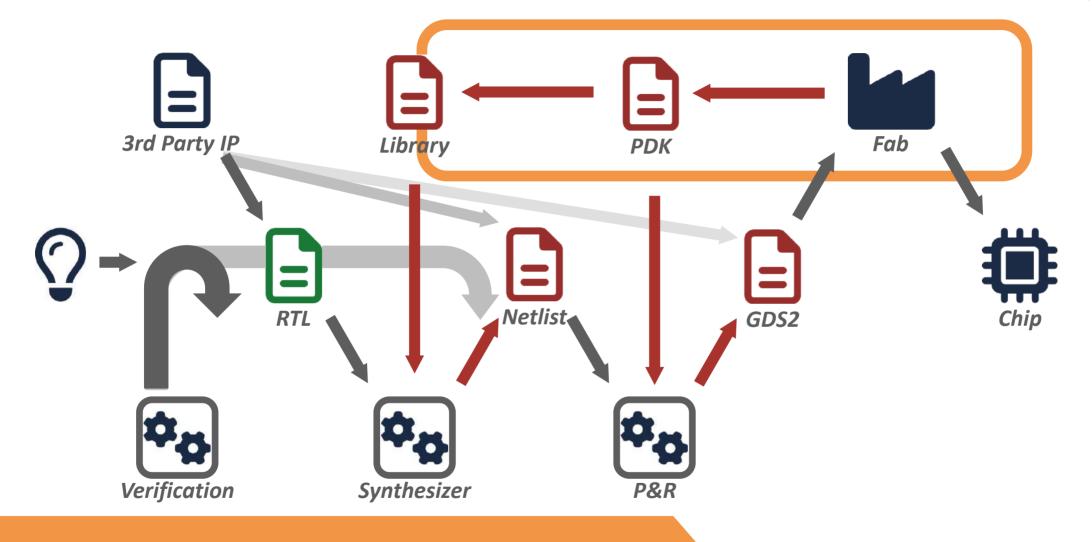

# Simplified IC design flow: proprietary tools

#### EDA vendors limit the output of their tools

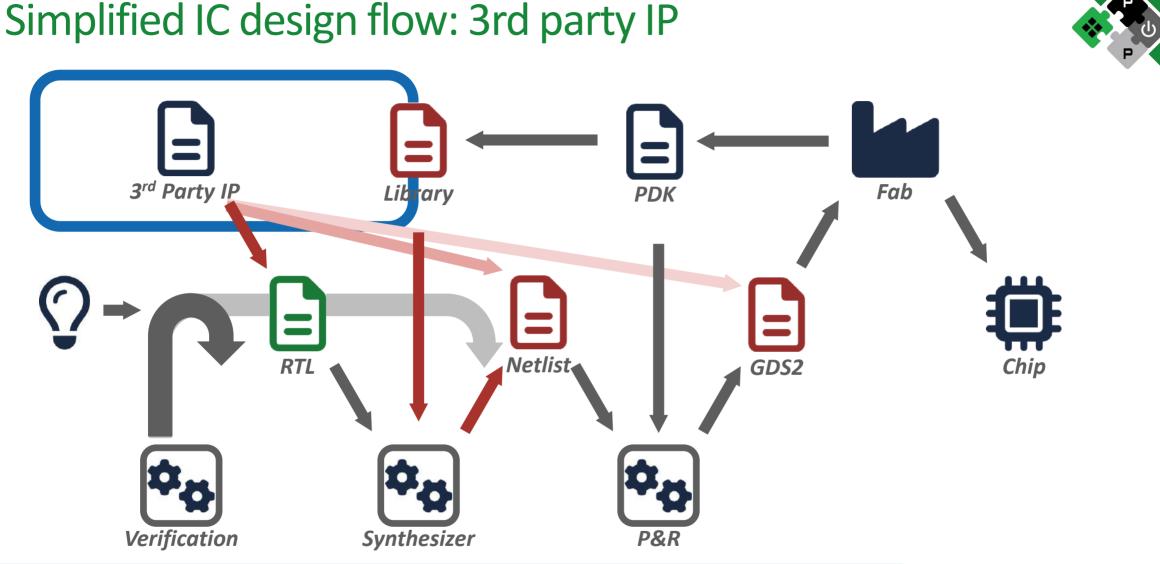

# Simplified IC design flow: technology provider

Fabs do not make PDK information accessible

3<sup>rd</sup> party IP when included can limit what can be open sourced

17

e Landscape

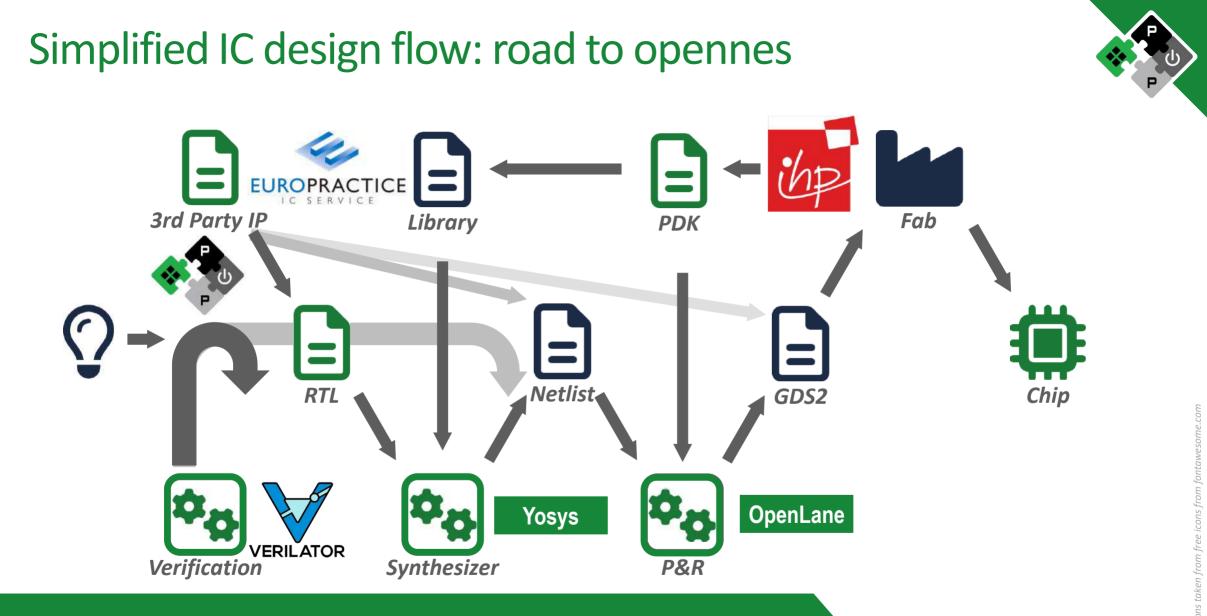

We are getting there, first fully open chips are underway

## Iguana, Linux capable fully-open RISC-V processor.

- Designed using IHP 130nm

- European Open PDK

- Tape-out July 2023

- Mostly open flow

- Some parts still rely on proprietary tools/IP

- Next version 4Q23 fully open

### What is PULP doing to maintain our cores?

- We (ETHZ and University of Bologna) are research groups

- Motivated to develop new architectures and systems

- We needed efficient RISC-V cores (and peripherals) for our work

- Not so good (or interested) in providing industrial level support for these cores

- We need help to

- Provide support

**ETH** zürich

- Develop industrial verification

- Governance of open source repositories

- Happy to receive this help from

ALMA MATER STUDIORU

- Open HW group (Ariane -> CVA6, RI5CY -> CV32E40P)

- LowRISC (ZeroRiscy -> Ibex)

- EU projects (Tristan/Isolde), Europractice

Frank K. Gürkaynak - PULP within the Open Source Hardware Landscape

### Open source HW is making great strides

- RTL level open source hardware is quite established

- (among others) PULP based solutions are widely used in Industry and Academia

- More openness requires solutions for Technology, EDA, 3rd party IP providers

- Open PDKs (slowly on the way)

- Open source EDA and/or more support from existing EDA vendors

- Lack of IP to make it harder to design impactful systems

- Efforts underway to support Open HW

- Non-profit organizations (OpenHW, RISC-V), EU projects (TRISTAN/ISOLDE), Supporting groups (Europractice)

- IC Design is an expensive business, there will always be a financial aspect

- Open source HW is an enabler, lowers costs and access, but does not make IC Design free

é Landscape

#### http://pulp-platform.org

#### @pulp\_platform