### PULP: 10 Years of Open Source Hardware

Integrated Systems Laboratory (ETH Zürich)

Frank K. Gürkaynak kgf@iis.ee.ethz.ch

**PULP Platform** Open Source Hardware, the way it should be!

@pulp platform pulp-platform.org 🥠 youtube.com/pulp\_platform

#### n Source Hardware

### Our latest design Occamy: 0.75 TFLOP/s, 400+ cores

- Chiplet based design

- 2x Compute chiplets (Occamy)

- 216+1 RISC-V cores

- GF12LPP

- Running at 1 GHz

- 2x 16GByte HBM memories

- Silicon Interposer (Hedwig)

- Finished in less than 15 months

How did we manage this?

• Taped out on 1<sup>st</sup> of July 2022

More on Occamy – talk by Gianna – Wed 14:15 – Chiplets for Al

### Open source hardware is for us a necessity

- Modern IC design like Occamy is complex and expensive

- We need partners to help and collaborate

- We need support (IPs, donations) to realize designs

#### **Open Source to the rescue**

- Makes it easy to collaborate with external partners, build teams (both industrial and academic)

- Less paperwork/NDAs to get started

- Partners see/are aware of what we provide

- What we do can be re-used (permissive licensing) by our partners

- Results can be more easily verified

### We started almost excatly 10 years ago (April 2013)

- Investigating new computing architectures

- Efficient over a wide range from IoT applications to HPC systems

- Key points

**ETH** zürich

- Parallel processing

- Near threshold computing

- Efficient switching between operating modes

- Making best use of technology

- Heterogeneous acceleration

- Parallel Ultra Low-Power (PULP) platform was born

Today the PULP team has grown to more than 70 people Headed by Luca Benini Teams in both ETH Zürich and University of Bologna ETH Zürich ALMA MATER STUDIOGNA ... and Bianca the Bear

ETH zürich () Alma mater studiorum

Frank K. Gürkaynak - PULP: 10 Years of Open Source Hardware

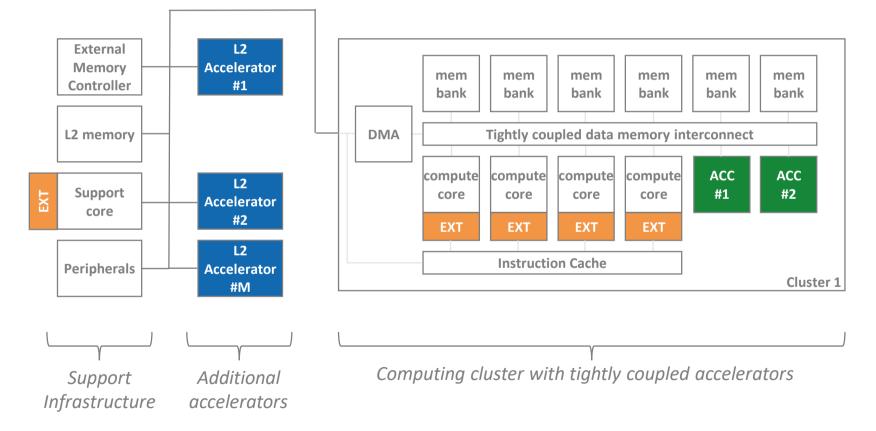

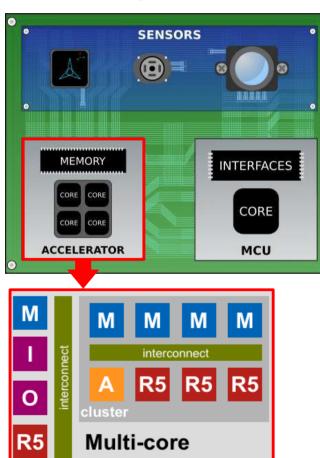

# Our research focus: cluster-based many-core accelerators

#### **Innovation factors**

**Extensions to processor cores**

- Explore new extensions

- Efficient implementations

#### **Shared-memory Accelerators**

- Domain specific

- Local memory

- **Multiple computing clusters**

- Communication

- Synchronization

High-speed on-chip interconnect (NoC, AXI, other..)

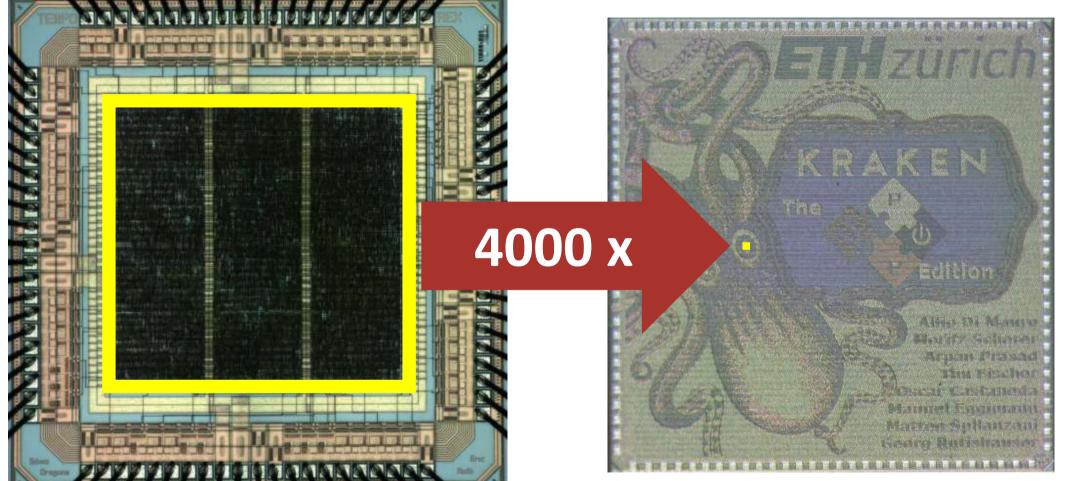

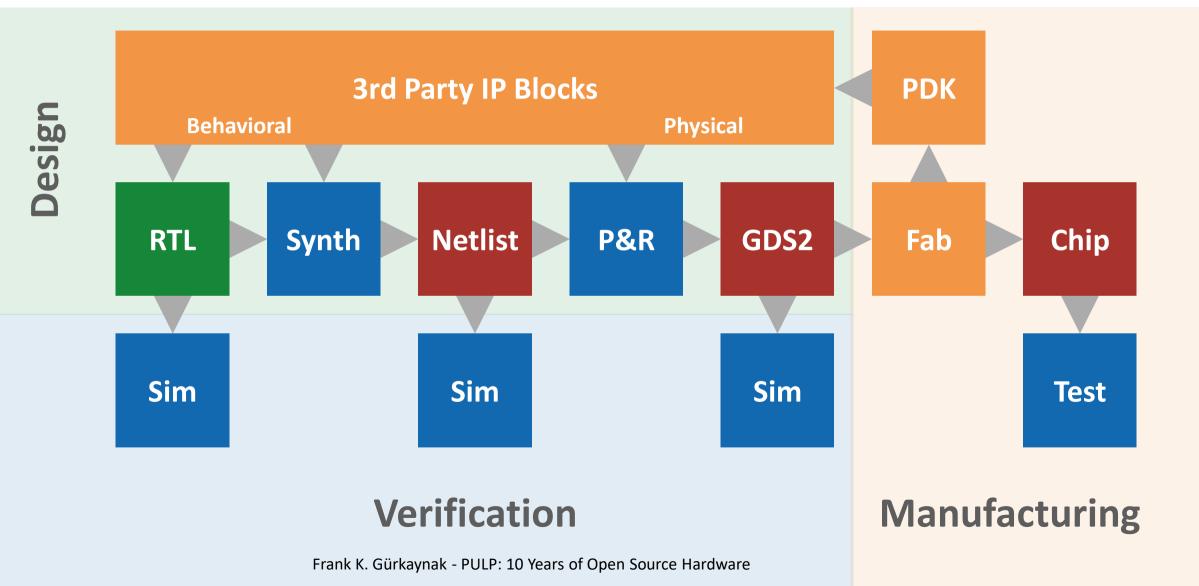

### In the last 20 years IC Design has changed a lot

What used to be a complete chip is now a small part of a SoC !

Source Hardware

$\circ$

3.3 mm

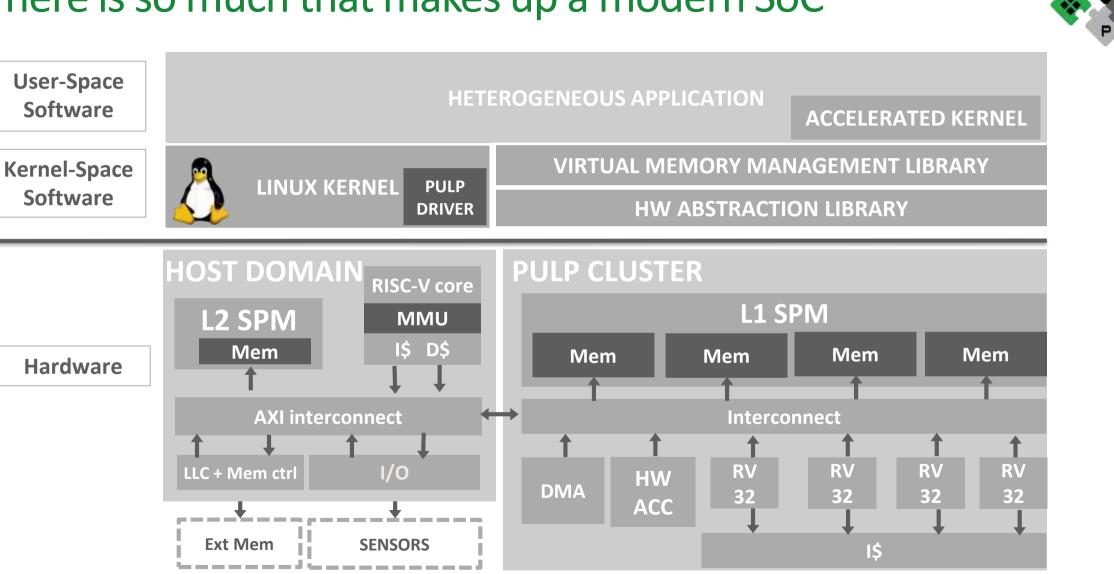

### There is so much that makes up a modern SoC

# In a typical design, innovation is only in a limited scope

#### **Open-source silicon-proven SoC template helps concentrate work where it counts**

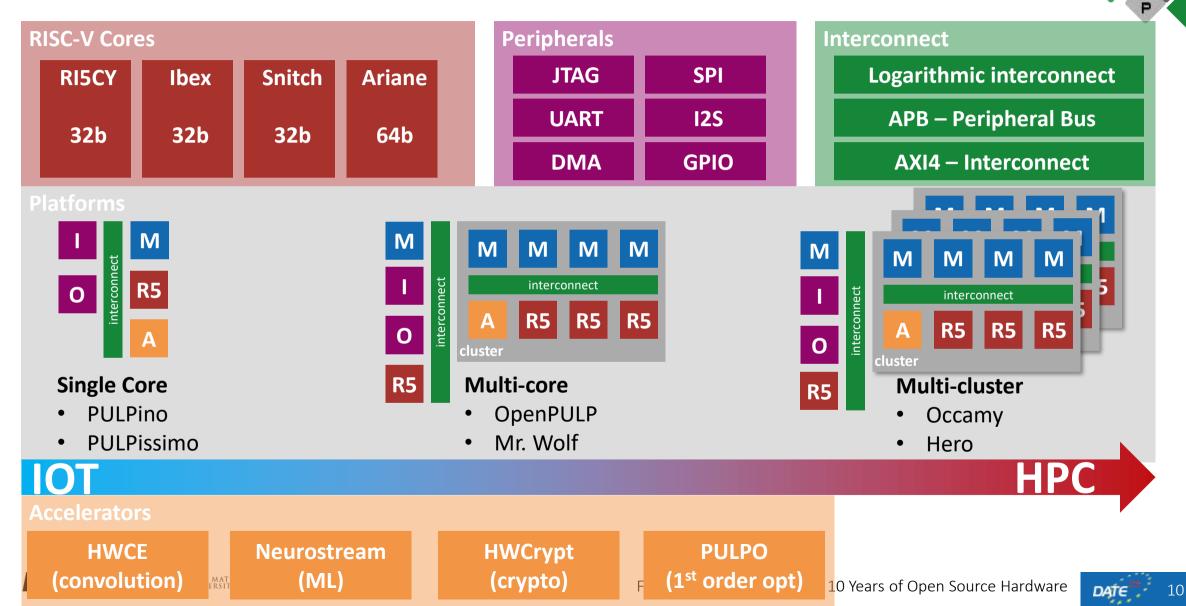

### What PULP provides is a box of building blocks

### Why is RISC-V so special: Freedom to Explore and Fail!

- The ISA provides a contract between HW and SW

- As long as you stick to the ISA, you can develop HW and SW independently

- All RISC-V research in HW can continue to rely on growing SW ecosystem for RISC-V

- **RISC-V** comes with plenty of options for extensions

- There are reserved encoding spaces for instruction set extensions

- Being able to change everything gives great flexibility

- Do you want 33 registers, or a 48 bit accumulator.. No problem

- You need to bring the SW support for your additions.

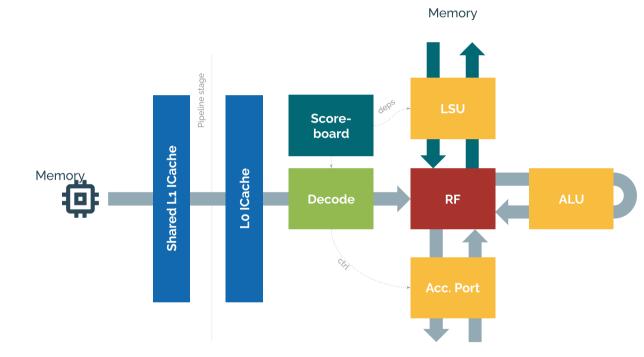

### What if we had a tiny 32b core

### **Introducing SNITCH**

- Start with a simple RISC-V core

- Focus on key features:

- Lightweight microarchitecture

- Extensibility: Performance through ISA extensions

- Latency tolerant

- Competitive frequency

- Around 15-25 kGE

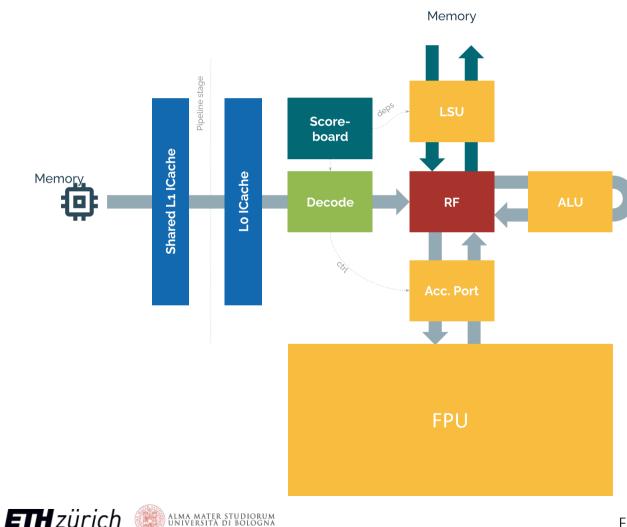

### What if we had a tiny 32b core and add a big 64b FPU

### **Introducing SNITCH**

- Start with a simple RISC-V core

- Focus on key features:

- Lightweight microarchitecture

- Extensibility: Performance through ISA extensions

- Latency tolerant

- Competitive frequency

- Around 15-25 kGE

- Capable 64b FPU with many extensions

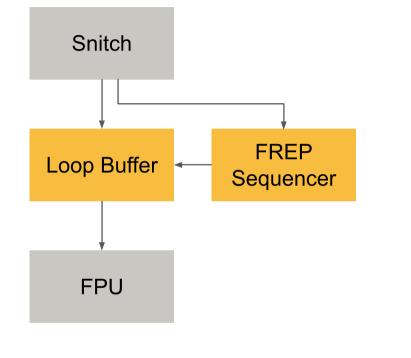

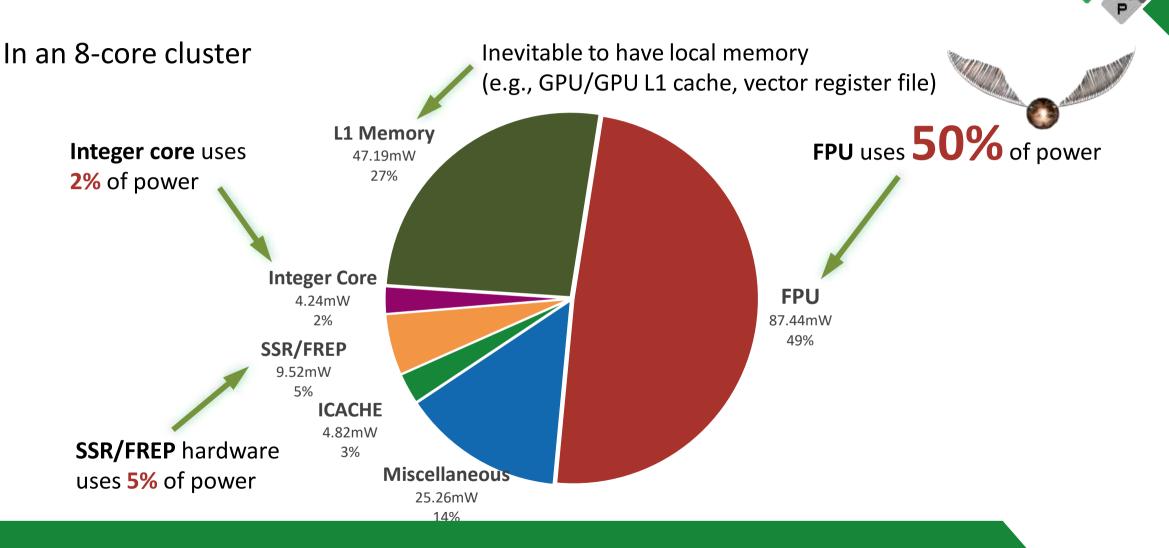

# What if we add a Floating-point Repetition Buffer? (FREP)

ALMA MATER STUDIORUM

ETH zürich

# mv r0, zero frep r1, 1 loop: addi r0, 1 loop: addi r0, 1 → fmadd r2, ssr0, ssr1 bne r0, r1, loop fmadd r2, ssr0, ssr1

#### Remove control flow overhead

- Programmable micro-loop buffer

- Sequencer steps through the buffer, independently of the FPU

- Integer core free to operate in parallel: Pseudo-dual issue

- High area- and energy-efficiency

Allows custom instruction set extensions

#### Frank K. Gürkaynak - PULP: 10 Years of Open Source Hardware

FPU:

— Cycles

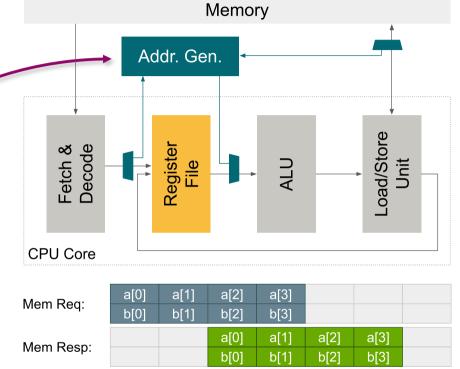

### What if we could stream data to from FPU directly? (SSR)

### Intuition: High FPU utilization $\approx$ high energy-efficiency

- Idea: Turn register R/W into memory loads/stores.

- Extension around the core's register file

- Address generation hardware

| loop:               | scfg 0, %[a], ldA    |

|---------------------|----------------------|

| <b>fld</b> r0, %[a] | scfg 1, %[b], ldB    |

| fld r1, %[b]        | loop:                |

| fmadd r2, r0, r1    | fmadd r2, ssr0, ssr1 |

- Increase FPU/ALU utilization by ~3x up to 100%

- SSRs ≠ memory operands

**ETH** zürich

Perfect prefetching, latency-tolerant

ALMA MATER STUDIORUN

FMA

[0]

FMA

[1]

FMA

[2]

FMA

### We have a processor that maximizes FPU efficiency

The flexibility of open ISA made it easy for us to explore such an approach

**DATE**<sup>23</sup> 16

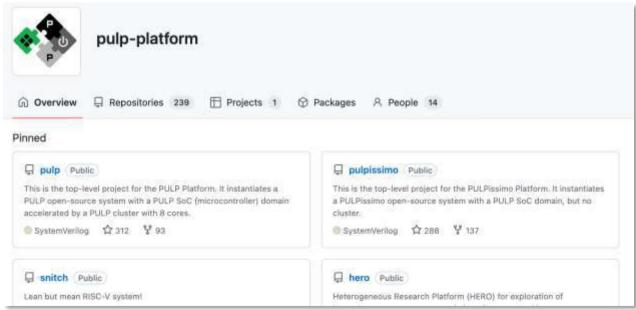

### PULP uses a permissive open source license

- All our development is on GitHub

- HDL source code, testbenches, software development kit, virtual platform

### <u>https://github.com/pulp-platform</u>

• Allows anyone to use, change, and make products without restrictions.

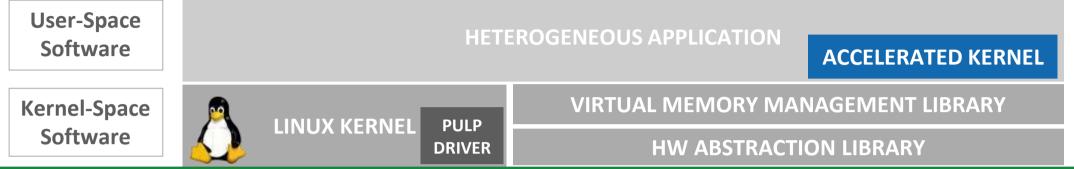

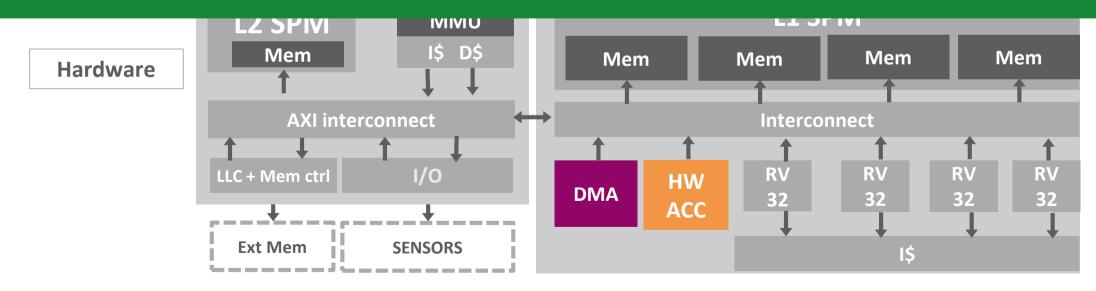

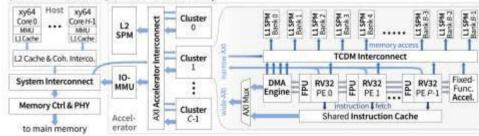

#### Heterogeneous Research Platform (HERO)

HERO is an FPGA-based research platform that enables accurate and fast exploration of heterogeneous computers consisting of programmable many-core accelerators and an application-class host CPU. Currently, 32-bit RISC-V cores are supported in the accelerator and 64-bit ARMv8 or RISC-V cores as host CPU. HERO allows to seamlessly share data between host and accelerator through a unified heterogeneous programming interface based on OpenMP 4.5 and a mixed-data-model, mixed-ISA heterogeneous compiler based on LLVM.

HERO's hardware architecture, shown below, combines a general-purpose host CPU (in the upper left corner) with a domain-specific programmable many-core accelerator (on the right side) so that data in the main memory (in the lower left corner) can be shared effectively.

### Open Source Hardware licensing still a critical issue

P B

- Two main flavors, divided opinion

- Permissive (Apache, MIT, BSD..): Favored by the industry, minimum obligations

- **Reciprocal** (GPL, LGPL,..): Feared by industry

- In theory, it should be possible to have reciprocal licensing for open hardware

- For example text of LGPL problematic for IC Design use.

- Cern OHL (<u>https://cern-ohl.web.cern.ch/</u>), comes in many flavors (reciprocal, permissive)

- Still more work needed, not many people understand issues of IC Design

- Lawyers (in companies) prefer well-known licenses (less work for them).

- PULP uses Solderpad (<u>http://solderpad.org/licenses/</u>)

- Permissive license based on Apache

- Clarifications for hardware use added by Andrew Katz

- Had no issues (so far) neither with academic nor industrial collaborations

### At the moment most of our Open Hardware is still only RTL

| ΤΥΡΕ                   | EXAMPLES     | STATUS       |

|------------------------|--------------|--------------|

| Open Specifications    | RISC-V       | Established  |

| Architectures          | PULP         | Quite mature |

| Implementations in RTL | Snitch, Hero | Many         |

| ΤΥΡΕ                   | EXAMPLES     | STATUS       |

|------------------------|--------------|--------------|

| Open Specifications    | RISC-V       | Established  |

| Architectures          | PULP         | Quite mature |

| Implementations in RTL | Snitch, Hero | Many         |

| Open source Hard IP    | FLL, DDR PHY | Very Limited |

|                        |              |              |

|                        |              |              |

| ΤΥΡΕ                           | EXAMPLES       | STATUS       |

|--------------------------------|----------------|--------------|

| Open Specifications            | RISC-V         | Established  |

| Architectures                  | PULP           | Quite mature |

| Implementations in RTL         | Snitch, Hero   | Many         |

| Open source Hard IP            | FLL, DDR PHY   | Very Limited |

| Process Design Kits Dependency | Skywater 130nm | Just Started |

|                                |                |              |

| ΤΥΡΕ                   | EXAMPLES       | STATUS       |

|------------------------|----------------|--------------|

| Open Specifications    | RISC-V         | Established  |

| Architectures          | PULP           | Quite mature |

| Implementations in RTL | Snitch, Hero   | Many         |

| Open source Hard IP    | FLL, DDR PHY   | Very Limited |

| Process Design Kits    | Skywater 130nm | On its way   |

| Open Source Tools      | Open Lane      | Quite usable |

### What is PULP doing to maintain our cores?

- We (ETHZ and University of Bologna) are research groups

- Motivated to develop new architectures and systems

- We needed efficient RISC-V cores (and peripherals) for our work

- Not so good (or interested) in providing industrial level support for these cores

- We need help to

- Provide support

- Develop industrial verification

- Governance of open source repositories

- Happy to receive this help from

- Open HW group (Ariane -> CVA6, RI5CY -> CV32E40P)

- LowRISC (ZeroRiscy -> Ibex)

- Others?

**ETH** zürich

### Academic open source $\rightarrow$ Industrial open source

- OpenHW Group is a not-for-profit, global organization (EU,NA,Asia) driven by its members and individual contributors where HW and SW designers collaborate in the development of open-source cores, related IP, tools and SW such as the Core-V family of cores.

- OpenHW Group provides an infrastructure for hosting high quality open-source HW developments in line with industry best practices.

ALMA MATER STUDIORUN

ETH zürich

## PULP has been used in all our publicly funded research

Swiss Funding (nano-tera)

ICYSoC

Near threshold computing

EU funded research projects **OPRECOMP**

*Approximate computing Multi-precision arithmetic*

European FPA **EPI / EUPilot** Snitch based accelerators

International projects **MITACS / Polara**

*Vector extensions for RISC-V processors*

European Processor Initiative

20

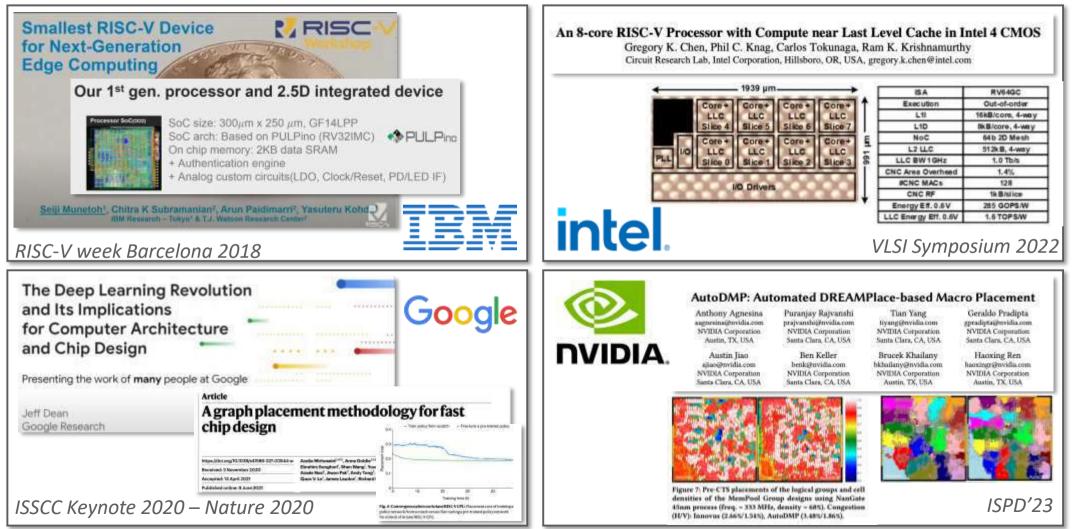

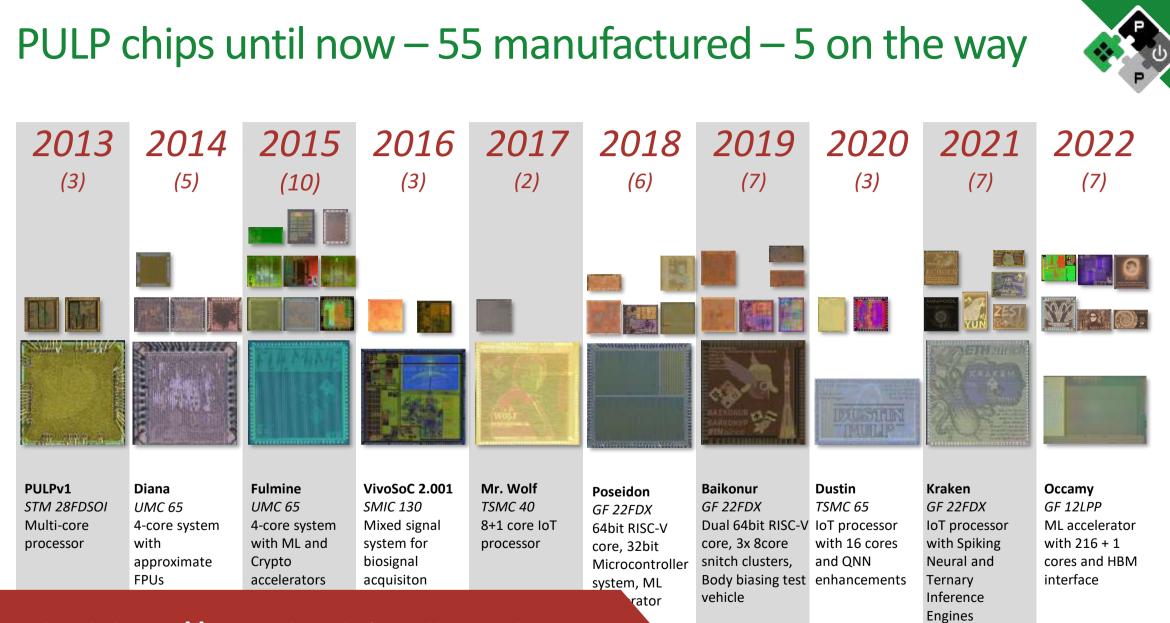

### **Industrial Collaborations**

#### Currently working with Meta, Intel, GF, IHP, PragmatIC, IIT

ears of Open Source Hardware

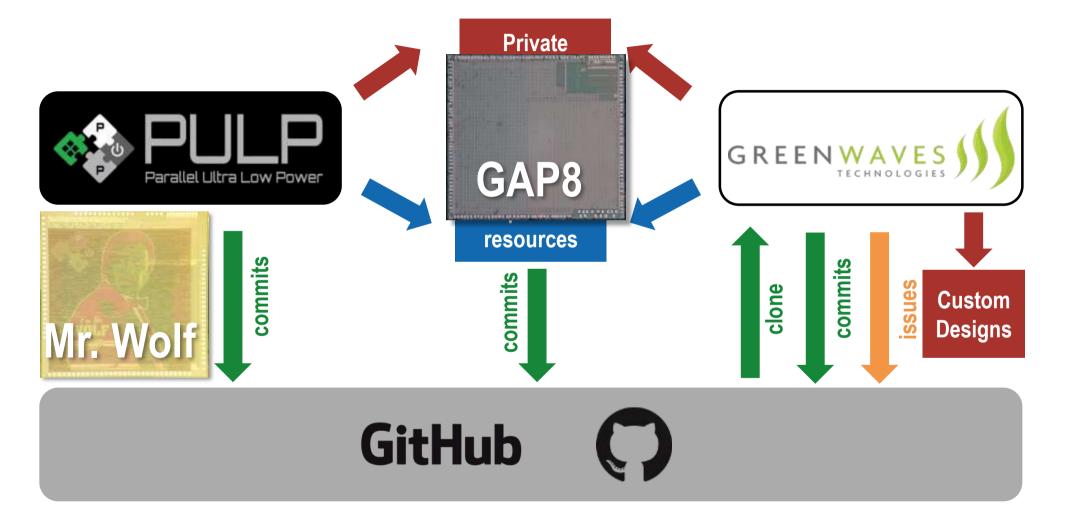

### Open source collaboration scheme explained

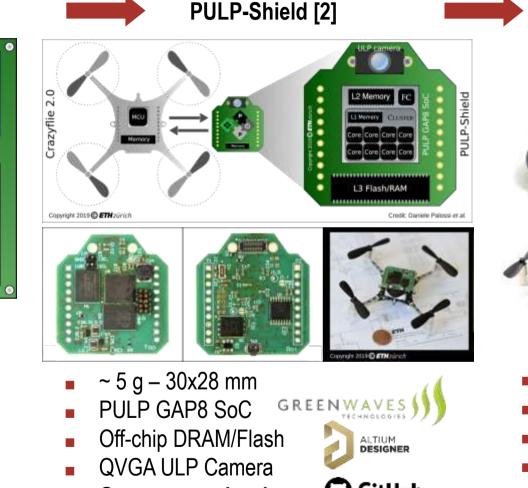

## The PULP-Based Commercial Nanodrone Platform

ULP heterogeneous model [1]

Al-deck

- ~8 g 40x28 mm

- PULP GAP8 SoC

- Off-chip DRAM/Flash

- QVGA ULP Camera

#### More on our work on Drones – talk by Lorenzo – Today 16:30

### So proud to have supported others in their research

**ETH** zürich

ALMA MATER STUDIORUM Università di Bologna

Frank K. Gürkaynak - PULP: 10 Years of Open Source Hardware

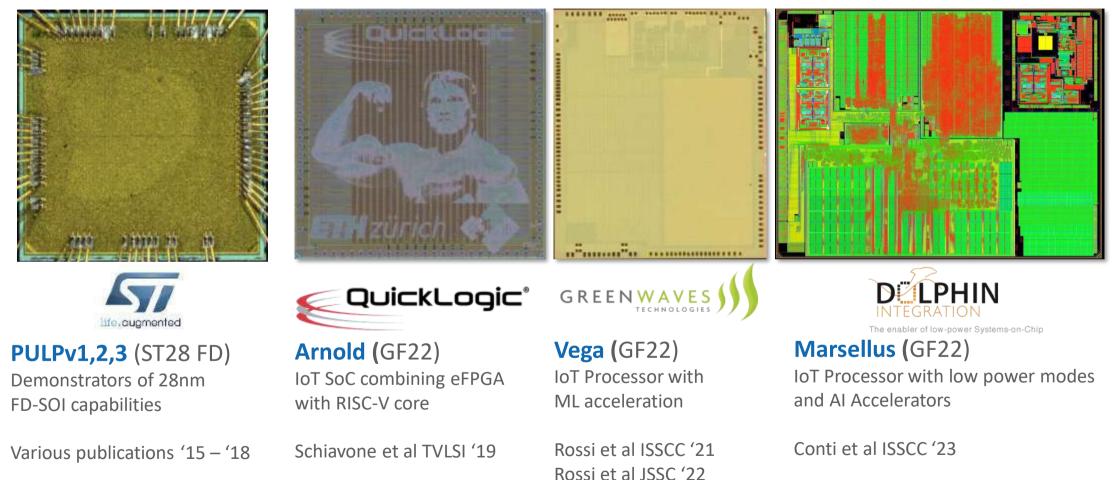

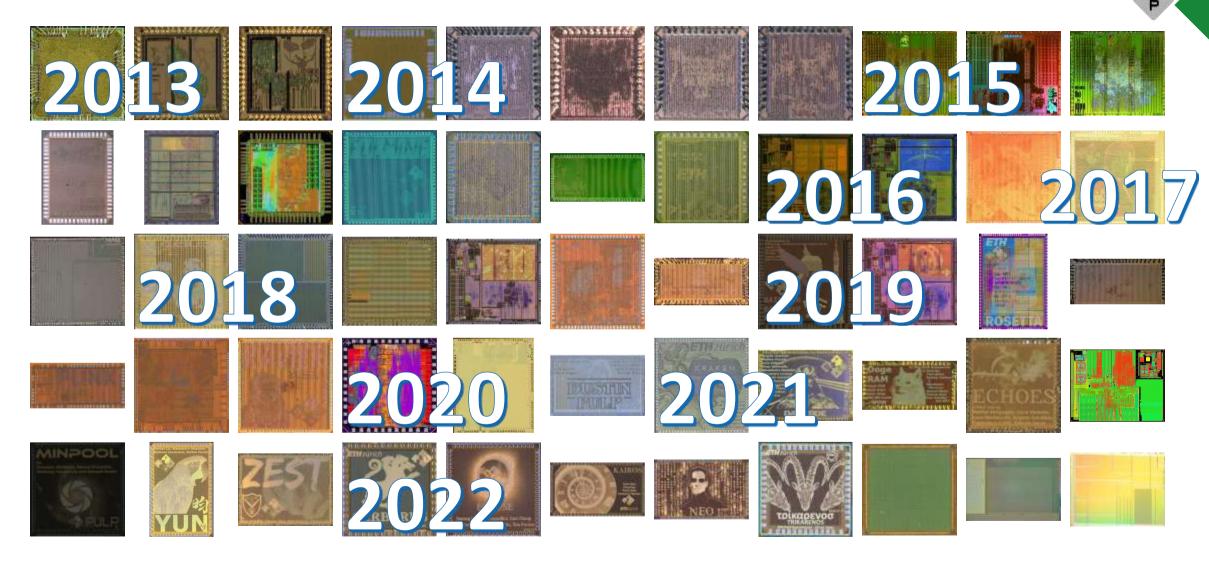

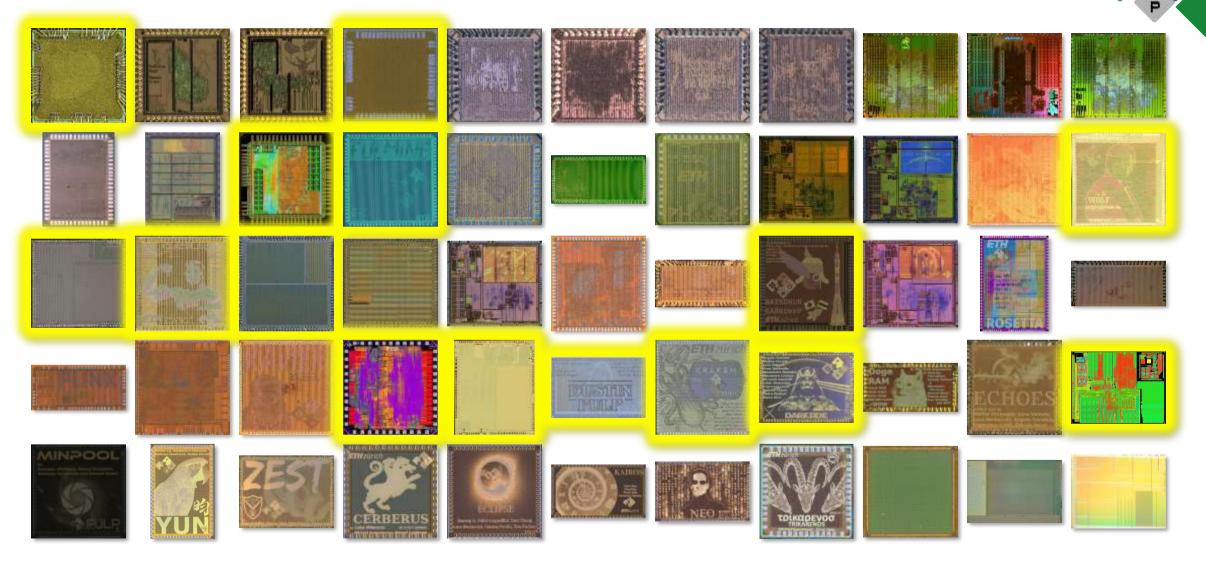

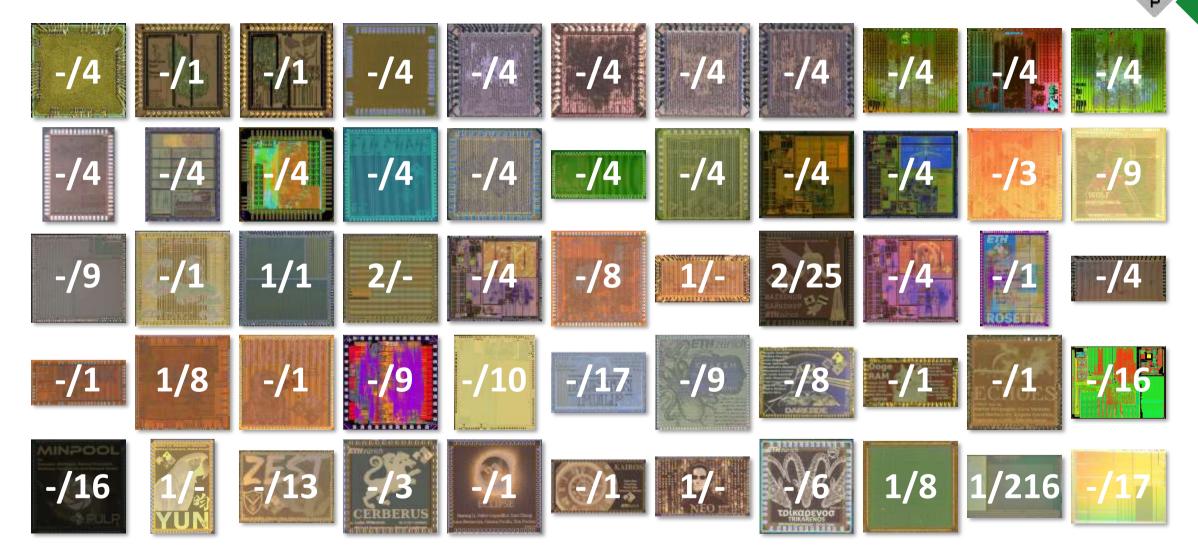

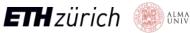

### PULP chips until now

### PULP chips until now – major publications

### PULP chips until now – 64b/32b cores

#### Check http://asic.ethz.ch for all our chips

### Coming soon from the PULP team

### A bit of a public service announcement

# **RISC-V Summit Europe** Barcelona RISC Join us in Barcelona – Registration open - https://riscv-europe.org/index.html **Monday-Friday** 5-9 June 2023

There is much more to come ...