# vCLIC: Towards Fast Interrupt Handling in Virtualized RISC-V Mixed-criticality Systems

The 42nd IEEE International Conference on Computer Design (ICCD 2024)

Enrico Zelioli Alessando Ottaviano Robert Balas Nils Wistoff Angelo Garofalo Luca Benini

ezelioli@iis.ee.ethz.ch aottaviano@iis.ee.ethz.ch balasr@iis.ee.ethz.ch nwistoff@iis.ee.ethz.ch agarofalo@iis.ee.ethz.ch lbenini@iis.ee.ethz.ch

@pulp\_platform >>

pulp-platform.org \*\*

youtube.com/pulp\_platform

#### **PULP Platform**

Open Source Hardware, the way it should be!

### **Motivation**

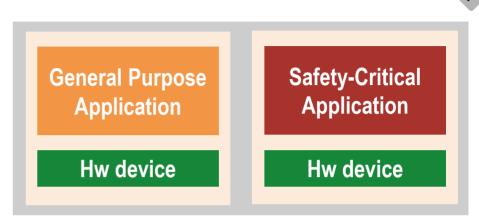

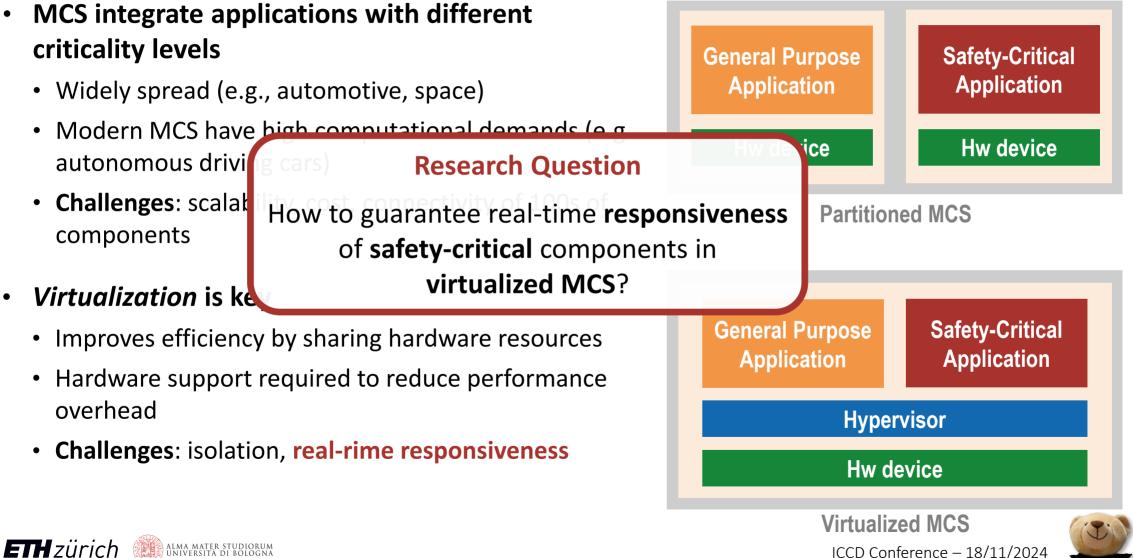

- MCS integrate applications with different criticality levels

- Widely spread (e.g., automotive, space)

- Modern MCS have high computational demands (e.g. autonomous driving cars)

- **Challenges**: scalability, cost, connectivity of 100s of components

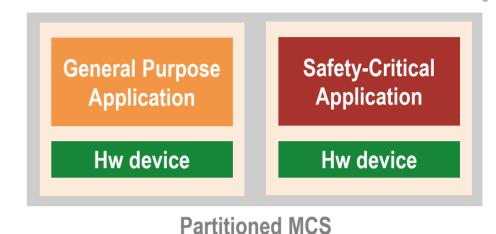

**Partitioned MCS**

## **Motivation**

- MCS integrate applications with different criticality levels

- Widely spread (e.g., automotive, space)

- Modern MCS have high computational demands (e.g. autonomous driving cars)

- **Challenges**: scalability, cost, connectivity of 100s of components

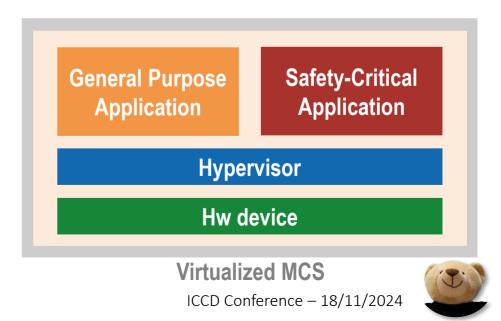

- Virtualization is key

- Improves efficiency by sharing hardware resources

- Hardware support required to reduce performance overhead

- Challenges: isolation, real-rime responsiveness

## **Motivation**

# Background

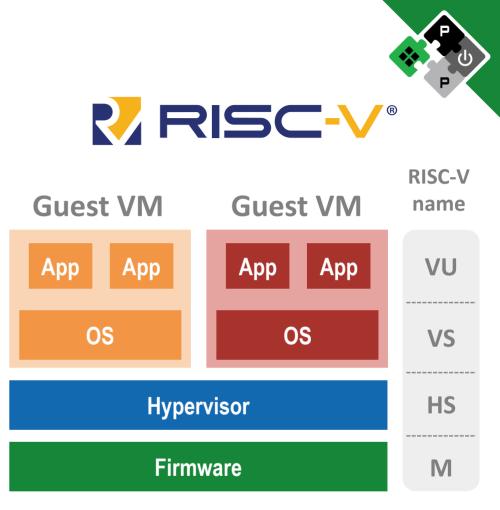

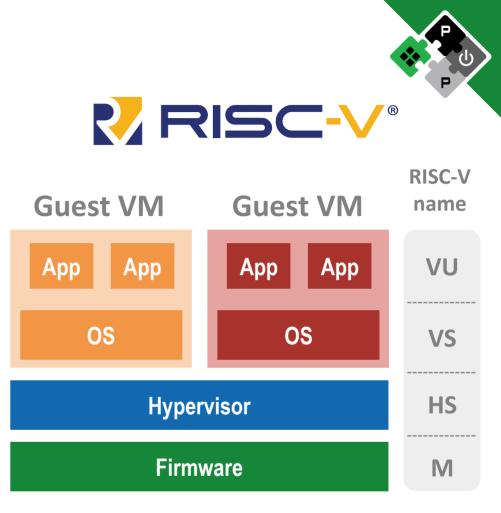

- RISC-V Mixed-Criticality Systems

- Open, modular ISA with wide range of applications

- Supports virtualization through dedicated Hypervisor extension

- Drives research in safety, security, real-time processing

**RISC-V Privilege Modes**

# Background

- RISC-V Mixed-Criticality Systems

- Open, modular ISA with wide range of applications

- Supports virtualization through dedicated Hypervisor extension

- Drives research in safety, security, real-time processing

- Interrupt virtualization

- Extends *hardware support* for virtualization to interrupt controller

- Enables direct injection of interrupts to VMs

- Reduces **interrupt latency** by minimizing hypervisor intervention

#### **RISC-V Privilege Modes**

- RISC-V base interrupt architecture [1]

- Original spec of interrupt

- Core-local + platform-level interrupt controllers

- RISC-V base interrupt architecture [1]

- Original spec of interrupt

**ETH** zürich

- Core-local + platform-level interrupt controllers

- Advanced Interrupt Architecture (AIA) [2]

- Designed for high-performance RISC-V systems

- Support for Message-Signaled Interrupts (MSI)

- Active research on embedded versions [3]

ALMA MATER STUDIORUM

<u>RISC-V Privileged Specification</u>

<u>RISC-V AIA Specification</u>

<u>"Interrupting" the Status Quo</u> (F. Marques et al.)

- RISC-V base interrupt architecture [1]

- Original spec of interrupt

- Core-local + platform-level interrupt controllers

- Advanced Interrupt Architecture (AIA) [2]

- Designed for high-performance RISC-V systems

- Support for Message-Signaled Interrupts (MSI)

- Active research on embedded versions [3]

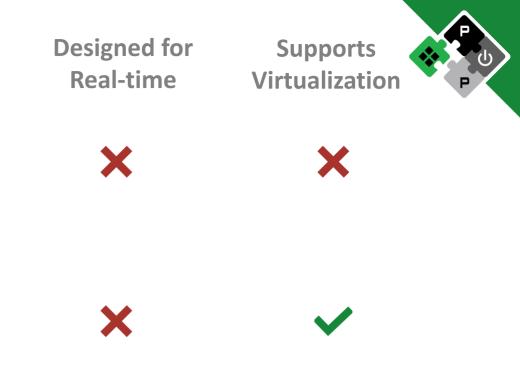

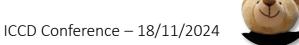

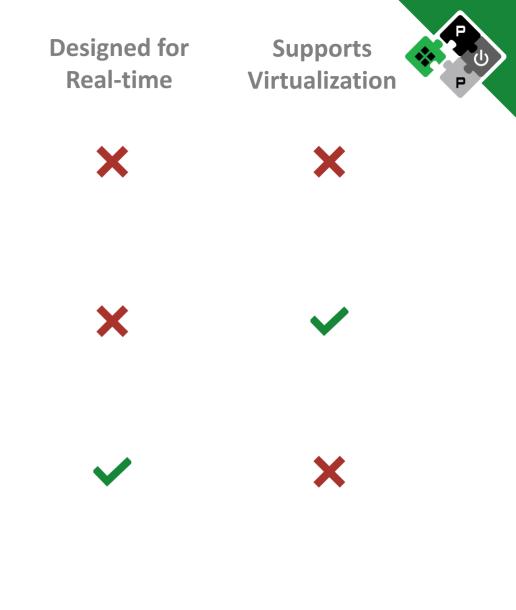

- RISC-V fast-interrupts (CLIC)

- Designed for fast interrupt response

- Interrupt vectoring, nesting, tail-chaining

- RISC-V base interrupt architecture [1]

- Original spec of interrupt

- Core-local + platform-level interrupt controllers

- Advanced Interrupt Architecture (AIA) [2]

- Designed for high-performance RISC-V systems

- Support for Message-Signaled Interrupts (MSI)

- Active research on embedded versions [3]

#### Our Work: vCLIC

**ETH** zürich

"Enable fast interrupt response in RISC-V virtualized MCS"

ALMA MATER STUDIORUN

ICCD Conference – 18/11/2024

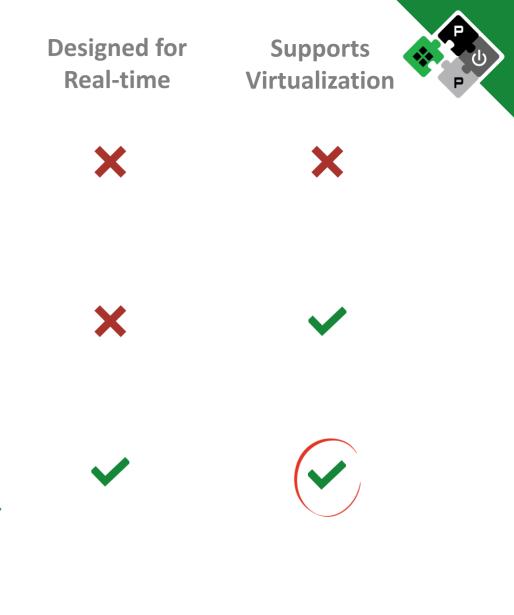

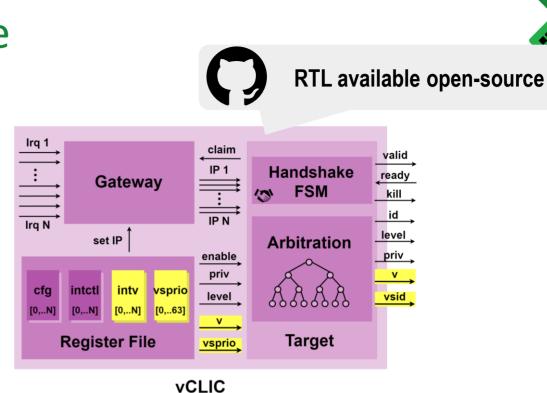

- Design principles

- Modularity

- VSCLIC: direct injection of interrupts

- VSPRIO: prioritization based on VM criticality

- Configurability

- Fine-grained tuning of resource utilization

- Compatibility

**ETH** zürich

Minimal deviation from CLIC spec\*

ALMA MATER STUDIORUM

vCLIC

- Design principles

- Modularity

- VSCLIC: direct injection of interrupts

- VSPRIO: prioritization based on VM criticality

- Configurability

- Fine-grained tuning of resource utilization

- Compatibility

**ETH** zürich

Minimal deviation from CLIC spec\*

ALMA MATER STUDIORUM

- Design principles

- Modularity

- VSCLIC: direct injection of interrupts

- VSPRIO: prioritization based on VM criticality

- Configurability

- Fine-grained tuning of resource utilization

- Compatibility

**ETH** zürich

Minimal deviation from CLIC spec\*

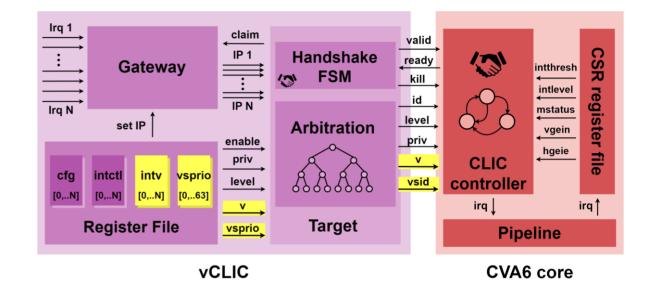

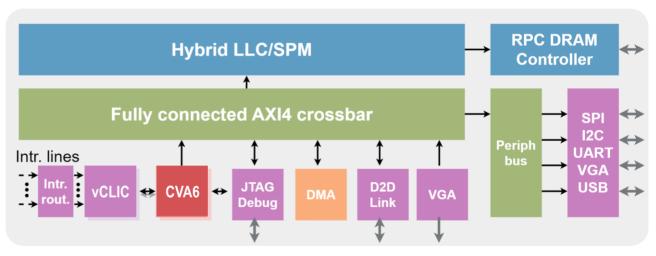

### System integration

- Coupled to CVA6 core

- Integrated in Cheshire SoC

- FPGA emulation for prototyping

ALMA MATER STUDIORUM

- Design principles

- Modularity

- VSCLIC: direct injection of interrupts

- VSPRIO: prioritization based on VM criticality

- Configurability

- Fine-grained tuning of resource utilization

- Compatibility

**ETH** zürich

Minimal deviation from CLIC spec\*

### System integration

- Coupled to CVA6 core

- Integrated in Cheshire SoC

- FPGA emulation for prototyping

ALMA MATER STUDIORUM

CVA6

- Design principles

- Modularity

- VSCLIC: direct injection of interrupts

- VSPRIO: prioritization based on VM criticality

- Configurability

- Fine-grained tuning of resource utilization

- Compatibility

**ETH** zürich

Minimal deviation from CLIC spec\*

### System integration

- Coupled to CVA6 core

- Integrated in Cheshire SoC

- FPGA emulation for prototyping

ALMA MATER STUDIORUM

#### **Cheshire SoC**

### • Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

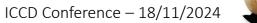

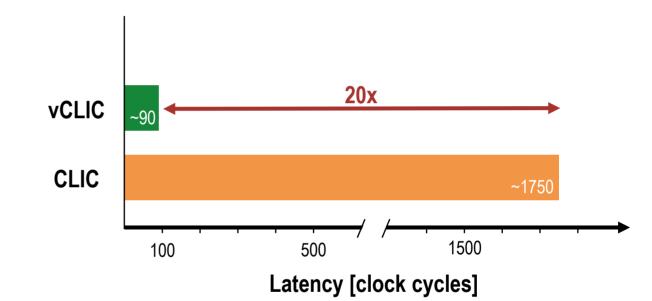

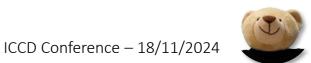

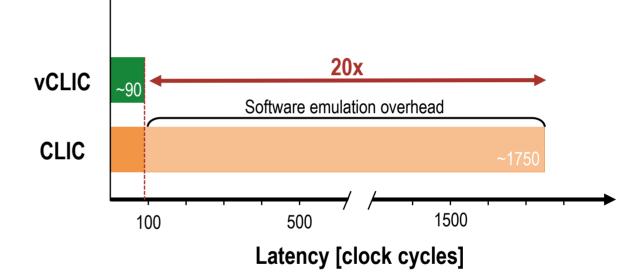

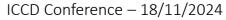

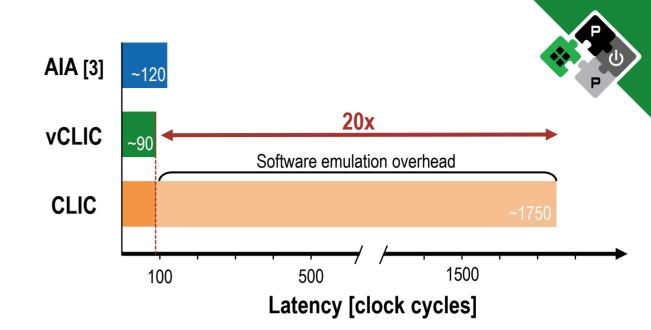

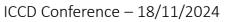

- Interrupt latency

- Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Interrupt latency

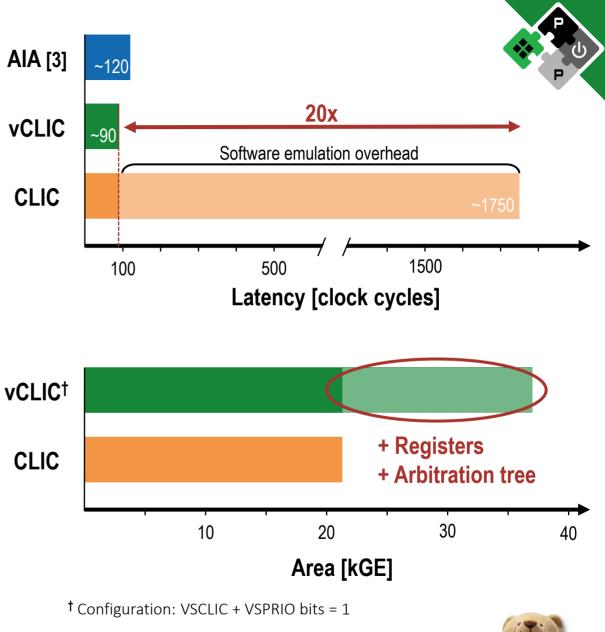

- **20x** reduced latency wrt software emulation

### Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Interrupt latency

**ETH** zürich

- **20x** reduced latency wrt software emulation

- Same interrupt latency as non-virtualized system

### Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Interrupt latency

**ETH** zürich

• **20x** reduced latency wrt software emulation

ALMA MATER STUDIORUM

Same interrupt latency as non-virtualized system

#### Software stack •

**Evaluation**

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2] •

- FreeRTOS, Linux •

- **Interrupt latency**

**ETH** zürich

• 20x reduced latency wrt software emulation

ALMA MATER STUDIORUM

Same interrupt latency as non-virtualized system

[1] Bao Hypervisor [2] Xvisor

- Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Interrupt latency

- **20x** reduced latency wrt software emulation

- Same interrupt latency as non-virtualized system

- Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Interrupt latency

- **20x** reduced latency wrt software emulation

- Same interrupt latency as non-virtualized system

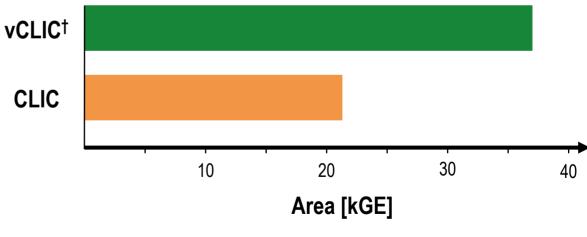

- Physical design\*

**ETH** zürich

• Minimal area overhead (<20kGE)

ALMA MATER STUDIORUN

- Iso-frequency with existing CLIC (>1GHz)

- \* Implemented in 16nm Intel technology

[3] "Interrupting" the Status Quo (F. Marques et al.)

<sup>†</sup> Configuration: VSCLIC + VSPRIO bits = 1

- Software stack

- OpenSBI firmware

- Bao hypervisor [1], Xvisor [2]

- FreeRTOS, Linux

- Interrupt latency

- **20x** reduced latency wrt software emulation

- Same interrupt latency as non-virtualized system

- Physical design\*

**ETH** zürich

• Minimal area overhead (<20kGE)

ALMA MATER STUDIORUN

- Iso-frequency with existing CLIC (>1GHz)

- \* Implemented in 16nm Intel technology

[3] <u>"Interrupting" the Status Quo</u> (F. Marques et al.)

## Conclusion

- We propose vCLIC:

- Virtualization extension of CLIC

- Up to 20x reduced interrupt latency wrt software emulation

- Limited area cost (<20kGE)

- First RISC-V interrupt controller designed for fast-interrupt response in virtualized systems

Our work is open-source at:

https://github.com/pulp-platform/clic

#### **PULP Platform** Open Source Hardware, the way it should be!

Q&A

Enrico Zelioli Alessandro Ottaviano Robert Balas Nils Wistoff Angelo Garofalo Luca Benini ezelioli@iis.ee.ethz.ch aottaviano@iis.ee.ethz.ch balasr@iis.ee.ethz.ch nwistoff@iis.ee.ethz.ch agarofalo@iis.ee.ethz.ch lbenini@iis.ee.ethz.ch

> @pulp\_platform 🎔 pulp-platform.org 🚸

**Institut für Integrierte Systeme – ETH Zürich** Gloriastrasse 35 Zürich, Switzerland

**DEI – Universitá di Bologna** Viale del Risorgimento 2 Bologna, Italy

**ETH**zürich () alma mater studiogum