# From an Open-Source ISA to Open-Source HW to Open-Source Silicon

Integrated Systems Laboratory (ETH Zürich)

Luca Bertaccini lbertaccini@iis.ee.ethz.ch

**PULP Platform**

Open Source Hardware, the way it should be!

@pulp\_platform >> pulp-platform.org

### Team of 100 people in ETH Zürich – University of Bologna

- Research on energy-efficient computing architectures

- Started in 2013, celebrated 10 years of PULP last year

- Led by Luca Benini

- Involves ETH Zürich (Switzerland) and University of Bologna (Italy)

- Large group of almost 100 people

#### ALMA MATER STUDIORUM Università di Bologna

### Team of 100 people in ETH Zürich – University of Bologna

• Research on energy-efficient computing architectures

#### We have designed and tested more than 60 PULP ICs 2014 2015 2016 2017 2018 2019 2020 2021 2013 2022 (3) (5) (3) (2) (6) (7) (3) (7) (9) (10)DUSTIN PULPv1 Fulmine VivoSoC 2.001 Mr. Wolf Baikonur Kraken Diana Dustin Occamy Poseidon STM 28FDSOI UMC 65 UMC 65 **SMIC 130** TSMC 40 GF 22FDX TSMC 65 GF 22FDX GF 12LPP GF 22FDX Dual 64bit RISC-V IoT processor Multi-core 4-core system 4-core system Mixed signal 8+1 core IoT IoT processor ML accelerator 64bit RISC-V with with ML and core. 3x 8core with Spiking with 216 + 1 system for with 16 cores processor processor core. 32bit Neural and Crypto biosignal snitch clusters. and QNN cores and HBM approximate Microcontroller FPUs accelerators acquisiton Body biasing test enhancements Ternary interface system, ML Inference vehicle rator Engines

#### Check http://asic.ethz.ch for all our chips

Foundation.

### We believe in open source

- Collaboration with many different domain experts

- We cannot afford to do everything in-house

- No long discussions on IP ownership and background IPs

- Everything in the open

- We can start right away

- Time is spent on design not necessary paperwork

- The licensing settles most of the needed discussions (who owns it, who can do what)

- Friendly licensing for commercial purposes

- Permissive licensing allows commercial exploitation, foreground of partners can be closed

- You can see what we have and evaluate us in advance

### Many benefits are enabled by open source

P D P

Managing Complex Designs

**Faster Collaborations**

**Facilitates Industry/Academia Relationships**

Auditable Designs, Reproducible Results

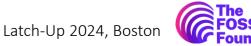

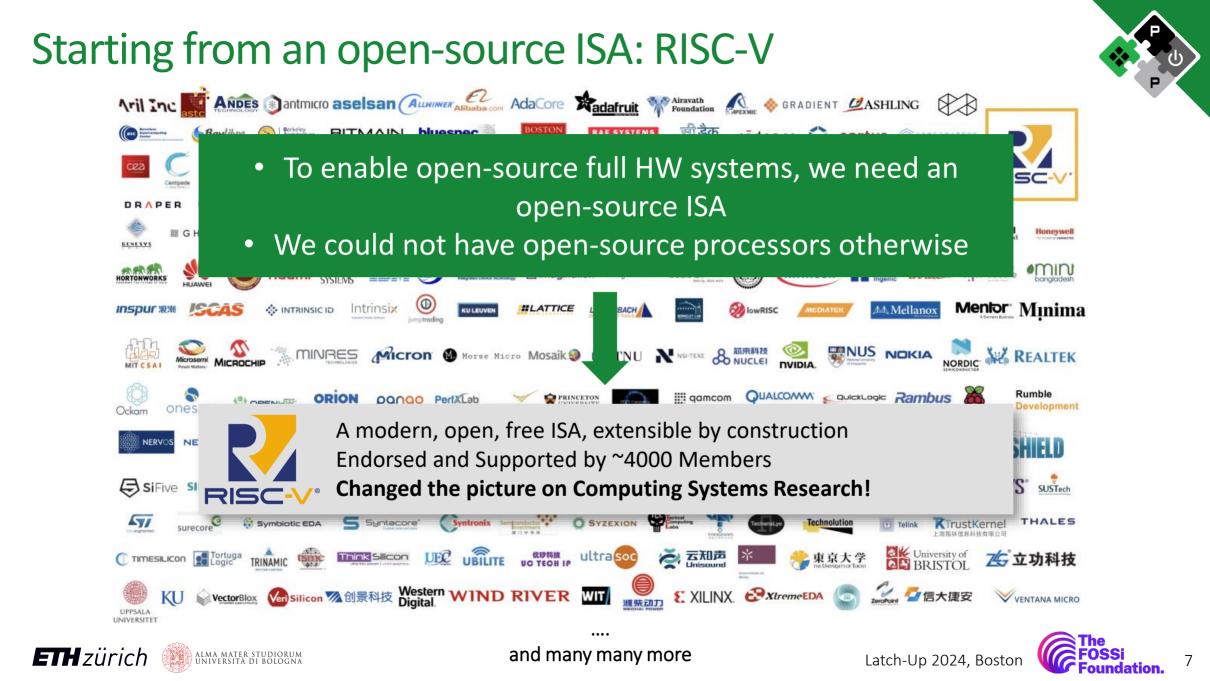

https://github.com/riscv/riscv-software-list

ETH zürich () alma mater studiorun

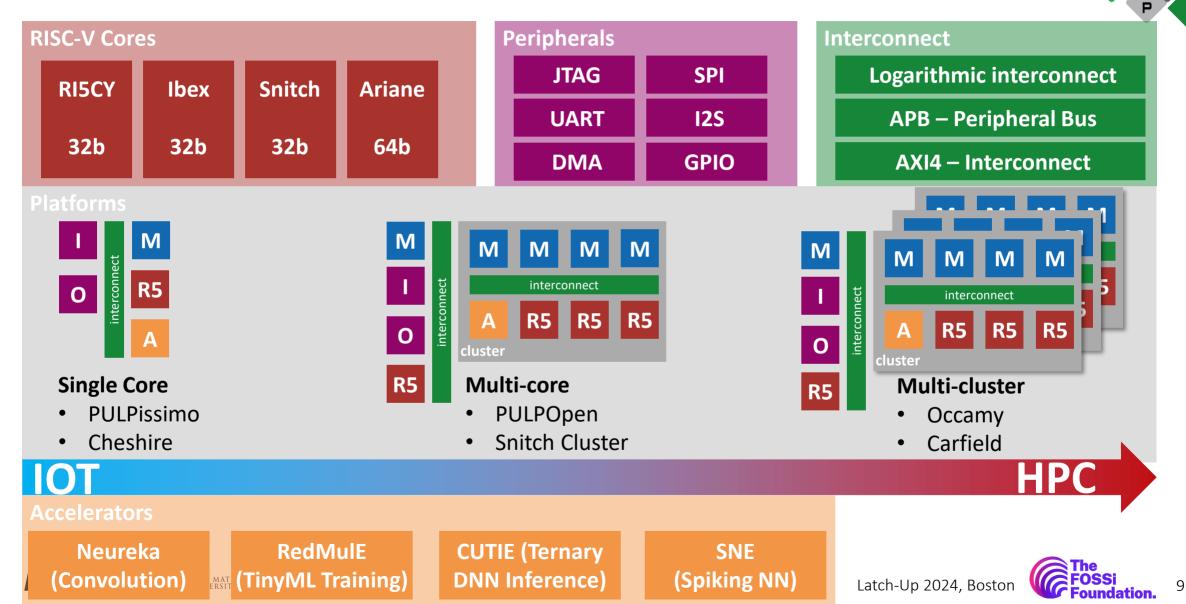

### What PULP provides is a box of building blocks

### All of our designs are open-source hardware

- All our development is on GitHub using a permissive license

- HDL source code, testbenches, software development kit, virtual platform

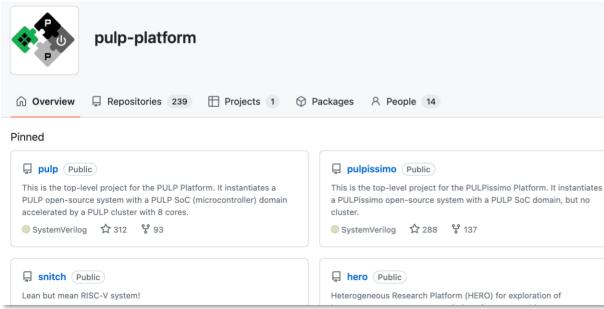

### https://github.com/pulp-platform

• Allows anyone to use, change, and make products without restrictions.

ALMA MATER STUDIORUM

**ETH** zürich

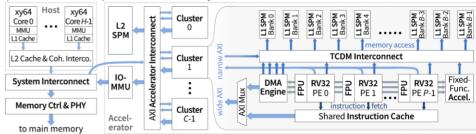

#### Heterogeneous Research Platform (HERO)

HERO is an **FPGA-based research platform** that enables accurate and fast exploration of **heterogeneous computers** consisting of **programmable many-core accelerators** and an **application-class host CPU**. Currently, 32-bit RISC-V cores are supported in the accelerator and 64-bit ARMv8 or RISC-V cores as host CPU. HERO allows to **seamlessly share data between host and accelerator** through a unified heterogeneous programming interface based on OpenMP 4.5 and a mixed-data-model, mixed-ISA heterogeneous compiler based on LLVM.

HERO's hardware architecture, shown below, combines a general-purpose host CPU (in the upper left corner) with a domain-specific programmable many-core accelerator (on the right side) so that data in the main memory (in the lower left corner) can be shared effectively.

### All of our designs are open-source hardware

- All our development is on GitHub using a perr a o

- HDL source code, testbenches, software development

### Many of the GitHub Trending SystemVerilog repositories for the past months are:

either directly from our groupor have originated in our group

hero Public

Heterogeneous Research Platform (HERO) for exploration of

| Explore                                                                                      | Q Type [] to search                                    | + • ⊙ m €                     |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------|

| lore Topics <b>Trending</b> Collections Events Gi                                            | Hub Sponsors                                           |                               |

| See what the GitHub                                                                          | Trending<br>community is most excited about this month |                               |

| Repositories Developers Sp                                                                   | oken Language: Any - Language: SystemVeril             | og + Date range: This month + |

| ☐ IowRISC / opentitan<br>DenTitan: Open source silicon root of trust                         |                                                        | 🛱 Star 👻                      |

| SystemVerilog 🏠 2,100 😵 647 Built by 🐑 🎒 🤀                                                   | 0                                                      | ☆ 43 stars this month         |

| pulp-platform / axi_mem_if                                                                   |                                                        | 🟠 Star 👻                      |

| SystemVerilog 🏠 29 😵 21 Built by 🎲 🕘 🧶 🧐 🤮                                                   |                                                        | ☆ 1 star this month           |

| pulp-platform / riscv-dbg<br>ISC-V Debug Support for our PULP RISC-V Cores                   |                                                        | 🛱 Star 👻                      |

| ISC-V Debug Support for our PULP RISC-V Cores<br>SystemVerilog 🏠 166 🦞 64 Built by 🌚 🍈 😨 🗿 🖲 |                                                        | ☆ 7 stars this month          |

| pulp-platform / axi2apb                                                                      |                                                        | ☆ Star →                      |

| )SystemVerilog 🏠 12 😵 19 Built by 🏀 🛞 😩 👘                                                    |                                                        | ជំ 0 stars this month         |

| pulp-platform / axi_riscv_atomics                                                            |                                                        | ☆ Star 👻                      |

| SystemVerilog 🏠 39 😵 11 Built by 🗿 🚱 🌍 🌍                                                     |                                                        | 1 0 stars this month          |

| pulp-platform / apb_node                                                                     |                                                        | 🟠 Star 👻                      |

| SystemVerilog 🏠 5 😵 17 Built by 🎲 😔 🕲 🌒                                                      |                                                        | ជំ 0 stars this month         |

| openhwgroup / cv32e40p                                                                       |                                                        | ☆ Star 👻                      |

**ETH** zürich

Snitch Public

Lean but mean RISC-V system

Latch-Up 2024, Boston

### The open model led to successful industry collaborations

QuickLogic®

GREENWAVES

### Meta **Nmem**

### **GlobalFoundries**<sup>™</sup>

Arnold (GF22) eFPGA with RISC-V core

ALMA MATER STUDIORUM

**ETH** zürich

Vega (GF22) IoT Processor with ML acceleration Siracusa (TSMC16) IoT Processor with NVM technology

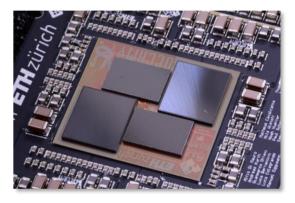

#### Occamy (GF12) Chiplet based ML accelerator with 432 RISC-V cores

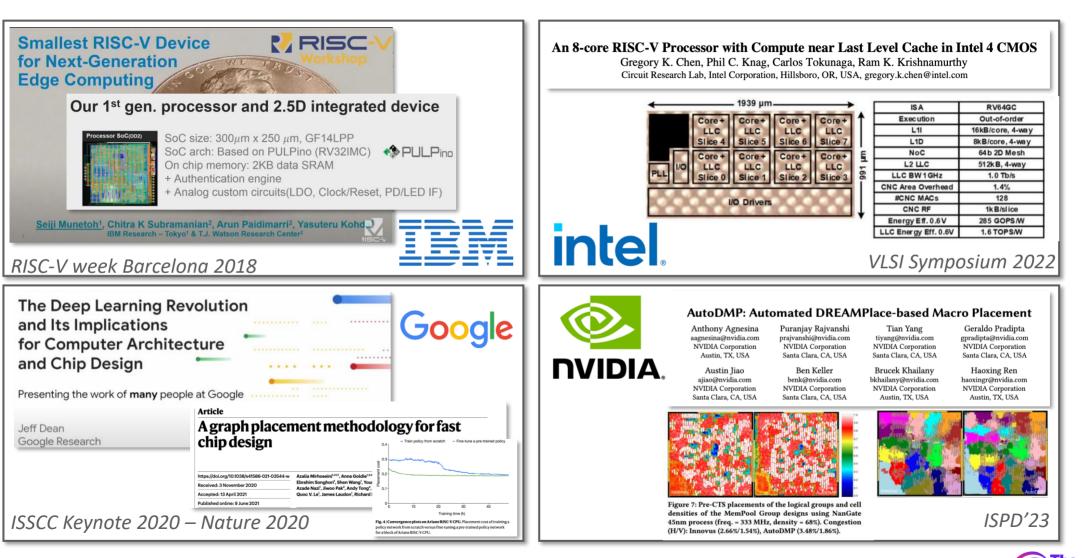

### And many have used our work for their research

### Some (surprising) side effects of open-source hardware

### There is a surprising amount of bureaucracy involved

- Code Ph.D. students/staff develop belongs to the university (they pay us)

- Master/semester thesis students own the work they produce

- Need to get proper approval for everyone involved

#### Most agreements with companies are not meant for open source

- Instead of paying for exclusive IP, we need sponsoring agreements

- Important to make sure we do not sign anything that binds our open-source effort

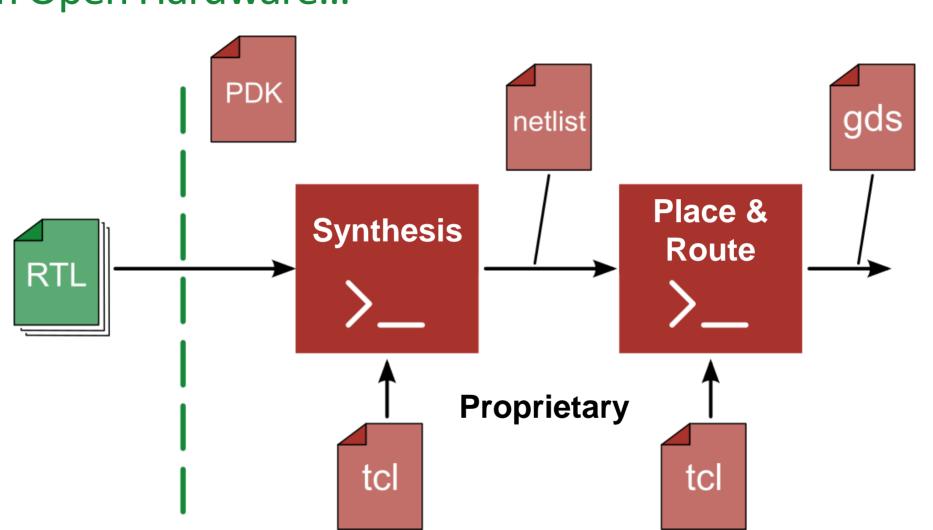

### From Open Hardware...

### ...to fully open-source IC design

16

### Benefits of end-to-end openness

- Research

- Easier collaboration (no NDAs)

- Reproducing results

- New research (using tools or data)

- Education

- Increased access

- Experiment with flows and tools

- No black boxes, full transparency

ALMA MATER STUDIORUN

Industry

**ETH** zürich

- Transparent chain of trust

- Lower initial cost

### Open-source PDKs are the key

- Physical designs will contain technology relevant information

- Nothing can be released (even if there were perfect open EDA tools) without technology info

- So no open PDK no open source releases beyond RTL/HLS code

- IPs containing proprietary information on technology cannot be released

- Open PDKs will allow us to change this

- Some good progress, more is needed

- Skywater (130nm), IHP (130nm)

- A 40nm/65nm open PDK would be a game changer, many viable products could be designed

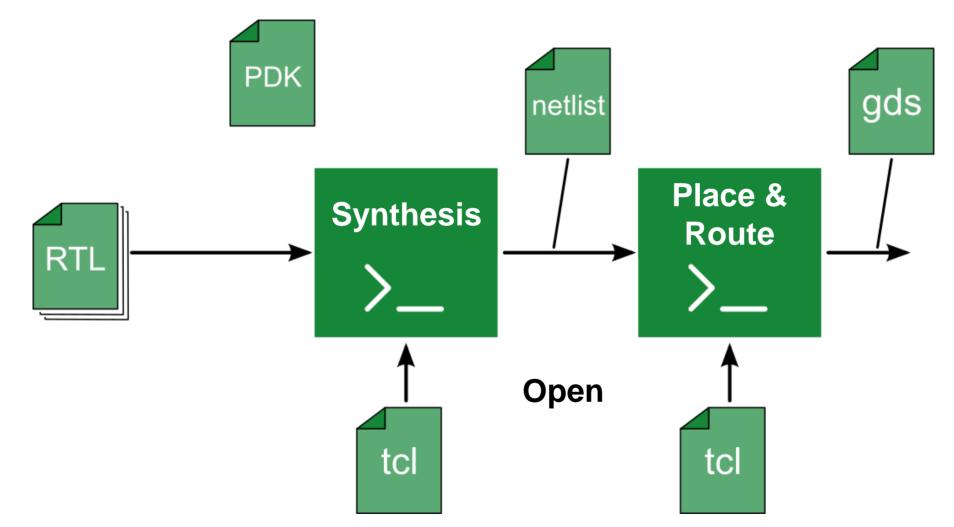

### **Open-source EDA tools**

- Open EDA tools work well and are improving fast

- ETHZ is actively collaborating with UCSD

- Currently working with Yosys (for synthesis) and OpenRoad (for PnR)

- Will not replace commercial EDA

- A gap to PPA, service, support will remain

- Open source EDA will allow you to make your own chips

- Good for many applications/needs

- Will be great for teaching

- Summer school at ETH Zürich

- June 3rd 7th

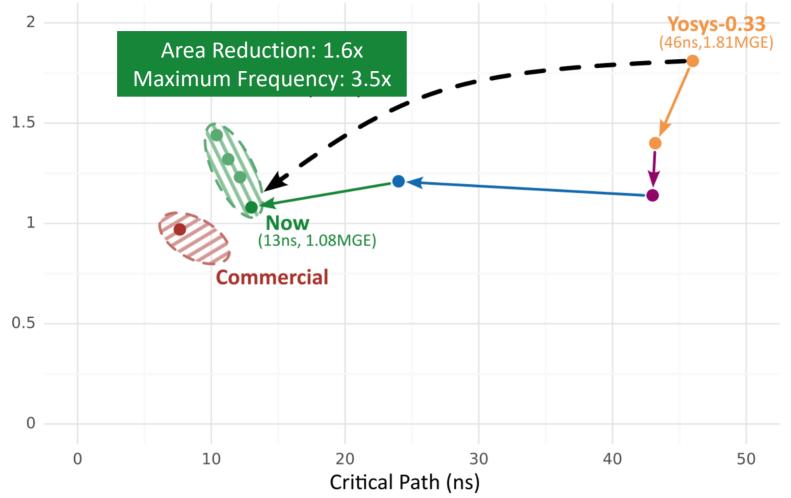

# Fully open IC design

20

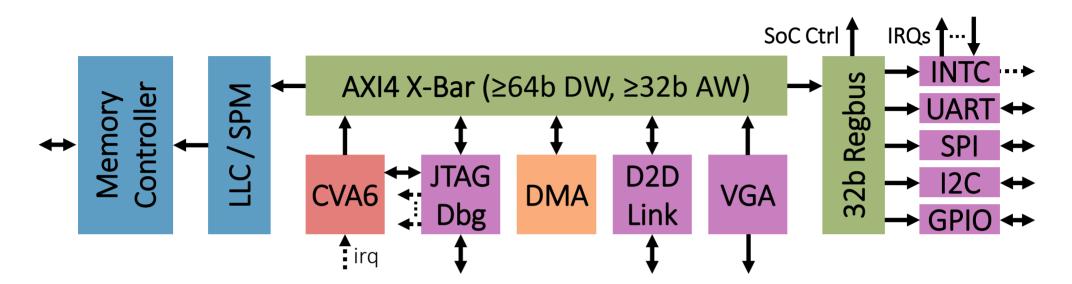

### System architecture

- An open-source Linux-capable RISC-V MPU (based on https://github.com/pulp-platform/cheshire)

- Including a 64-bit RISC-V core (CVA6 -https://github.com/openhwgroup/cva6)

- About 1 MGE of logic

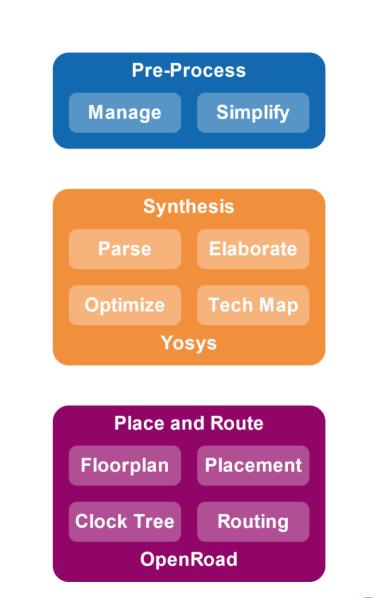

### **Open-source tool-flow**

• Open-Source PDK (IHP 130nm)

#### • Pre-Process

- Simplify SystemVerilog

- Convert to Verilog

#### Synthesis

**ETH** zürich

• Yosys from RTL to generic-cells

ALMA MATER STUDIORUN

- Calls ABC for logic optimization and mapping

- Place-and-Route

- Collection of research tools into OpenRoad

22

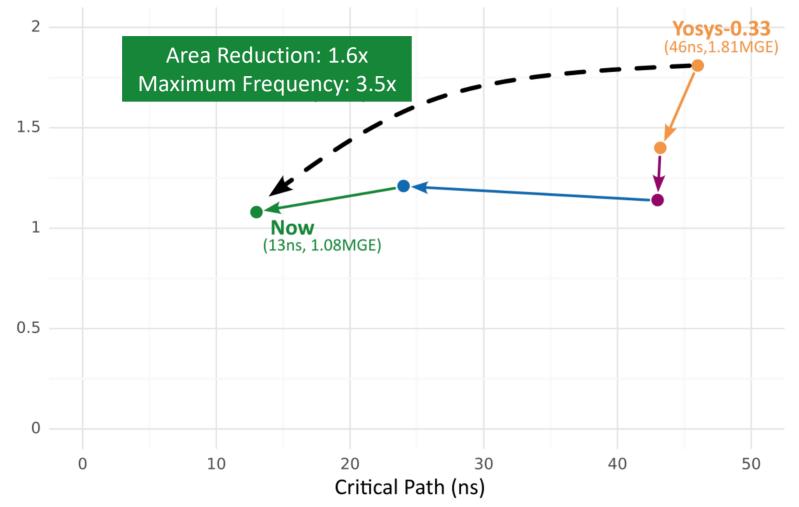

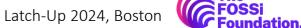

#### Massive PPA improvements in 6 months Logic Area (MGE) 2 Yosvs-0.33 (46ns 1.81MGE 1.5 1 Now (13ns, 1.08MGE) 0.5 0 10 50 20 30 40 n Critical Path (ns)

IHP130, tt-corner; Yosys-0.37 with optimized script if not mentioned otherwise

ETH zürich alma mater studiorum università di Bologna

### Massive PPA improvements in 6 months

Logic Area (MGE)

IHP130, tt-corner; Yosys-0.37 with optimized script if not mentioned otherwise

ETH ZÜRİCH (E) ALMA MATER STUDIORUM UNIVERSITA DI BOLOGNA

### Massive PPA improvements in 6 months

Logic Area (MGE)

IHP130, tt-corner; Yosys-0.37 with optimized script if not mentioned otherwise

ETH zürich alma mater studiorum università di bologna

Latch-Up 2024, Boston

## In a nutshell: why open-source hardware & silicon?

- It is a necessity

- We can not afford to make everything ourselves, we need to collaborate

- Makes it possible to work together quickly

- Your results are more trustworthy, anybody can verify it!

- It works

- We have more projects, and more funding due to our open-source activities

- We were able to start many interesting and fruitful collaborations

- It helps others as well

- Many companies, universities, individuals are using pieces of PULP

- There is already significant commercial use, a lot we don't even know about

### The future of open-source silicon is bright!