# ETH zürich

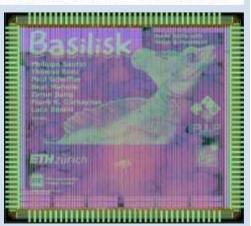

## Basilisk: Achieving Competitive Performance with Open EDA Tools on an Open-Source Linux-Capable RISC-V SoC

Philippe Sauter<sup>1</sup>, Thomas Benz<sup>1</sup>, Paul Scheffler<sup>1</sup>, Zerun Jiang<sup>1</sup>, Beat Muheim<sup>1</sup>, Frank K. Gürkaynak<sup>1</sup>, Luca Benini<sup>1,2</sup> <sup>1</sup>Integrated Systems Laboratory, ETH Zurich <sup>2</sup>Department of Electrical, Electronic, and Information Engineering, University of Bologna

#### 1 Introduction and Motivation

- OS EDA flow profits multiple communities

- Academia: NDA-free and open collaboration

- Education: Limit-free understanding of the EDA tools

- Industry: Transparent chain-of-trust, more skilled personal

- OS EDA flows exist, achieving **good** results for **small** designs

- Flows and tools show cracks with multi-million-gate designs

Cheshin

- No end-to-end open Linux-capable SoC yet

- Basilisk SoC

- Cheshire SoC platform<sup>[1]</sup>

- Linux-capable

- CVA6 64-bit RISC-V

- USB 1.1 host

- VGA display

- External, digital-only

DRAM interface

- Implement Basilisk end-to-end open (Yosys, OpenROAD)

- Improving OS EDA tools and flow along the journey

SV2V

Yosys

Realistic benchmark for OS EDA tools to grow

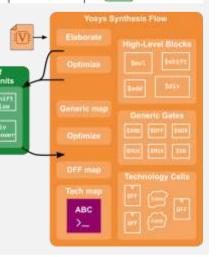

## 2 Synthesis Improvements

- Part-select operation in Yosys

- Prior to v0.34: barrel **shifter**

- More complex than mux

- High-cost gate-level netlist

- **Contributed** fix in v0.36

- Opt. pass inferring MUX

|          | Code                                                                     | Graphical  |

|----------|--------------------------------------------------------------------------|------------|

| e        | out(sel)                                                                 |            |

| ,        | out[9*sel+:9]                                                            |            |

| s<br>vel | <pre>\$shiftx(<br/>.A(out),<br/>.B(-9+sel),<br/>.Y(out_sel)<br/>);</pre> |            |

| s<br>ic  | <pre>module shiftx(); \$MUX()</pre>                                      | selváblaði |

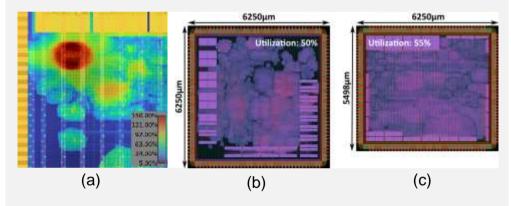

## 3 Place & Route Improvements

- Focus on OpenROAD's flow scripts

- Improved sequence of commands

- Hyperparameter tuning to reduce density hotspots

- Density force: push cells to achieve target density

- Wire force: attract connected cells to reduce wire length

- (a) example of over 100% density at the site of the bootrom

- Untuned (b) and tuned (a) hyperparameters

- Our flow results in more uniform density without hotspots

## 4 Results and Conclusion

- Improve flow:

- **1.6x** in area

- 2.3x in timing

- Taped Basilisk in May 2023

- First end-to-end open Linux-capable SoC

|                       | Yosys-0.33 | MUX     | ABC     | LAU     |

|-----------------------|------------|---------|---------|---------|

| Logic area            | 1.8 MGE    | 1.4 MGE | 1.1 MGE | 1.1 MGE |

| Timing                | 33 MHz     | 37 MHz  | 71 MHz  | 77 MH2  |

| Logic levels *        | 182 LL     | 149 LL  | 54 LL   | 51 LL   |

| Runtime <sup>b</sup>  | 5.4 h      | 2.8 h   | 2.2 h   | 2.2 h   |

| Peak RAM <sup>c</sup> | 217 GB     | 105 GB  | 76 GB   | 75 GB   |

#### • 1.5x in area, 2.9x in RAM

- ABC: optimized scripts

- Lazy man's synthesis

- Cheaper optimization run multiple times

- 2.3x in timing

- Library of arithmetic units<sup>[2,3]</sup>

- Arithmetic operator replacement

- Optimized open-source library<sup>[3]</sup>

- Room for improvement

- Timing-driven synthesis

- Automatic hyperparameter tuning

#### References

- Ottaviano et al., Cheshire: A Lightweight, Linux-Capable RISC-V Host Platform for Domain-Specific Accelerator Plug-In, IEEE TCAS-II, 2023

- 2. VHDL Library of Arithmetic Units: https://iis-people.ee.ethz.ch/~zimmi/arith\_lib.html

- $\label{eq:linear} \textbf{3. Library of arithmetic units: https://github.com/pulp-platform/ELAU}$