### Industry Academia Collaborations on Open-Source Hardware

Integrated Systems Laboratory (ETH Zürich)

Frank K. Gürkaynak kgf@iis.ee.ethz.ch

@pulp\_platform > pulp-platform.org & youtube.com/pulp platform

**PULP Platform**

Open Source Hardware, the way it should be!

## PULP Platform by ETH Zürich and University of Bologna

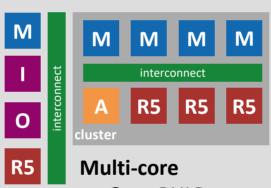

OCCAMY

432 RISC-V cores

Chiplets

GF12nm

1GHz

Occamy: A 432-Core 28.1 DP-GFLOP/s/W 83% FPU Utilization Dual-Chiplet, Dual-HBM2E RISC-V-based Accelerator for Stencil and Sparse Linear Algebra Computations with 8-to-64-bit Floating-Point Support in 12nm FinFET

How do we manage to design projects of this size at a University?

er.\* Manuel Eggimann,\*

erco Ottavi,‡

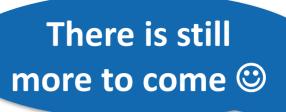

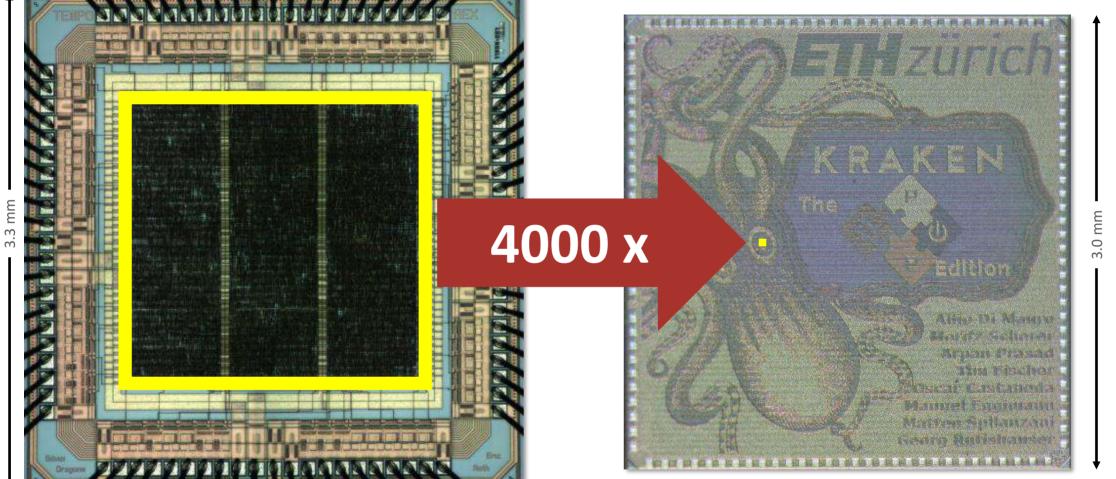

### In 11 years PULP team has designed more than 60 chips

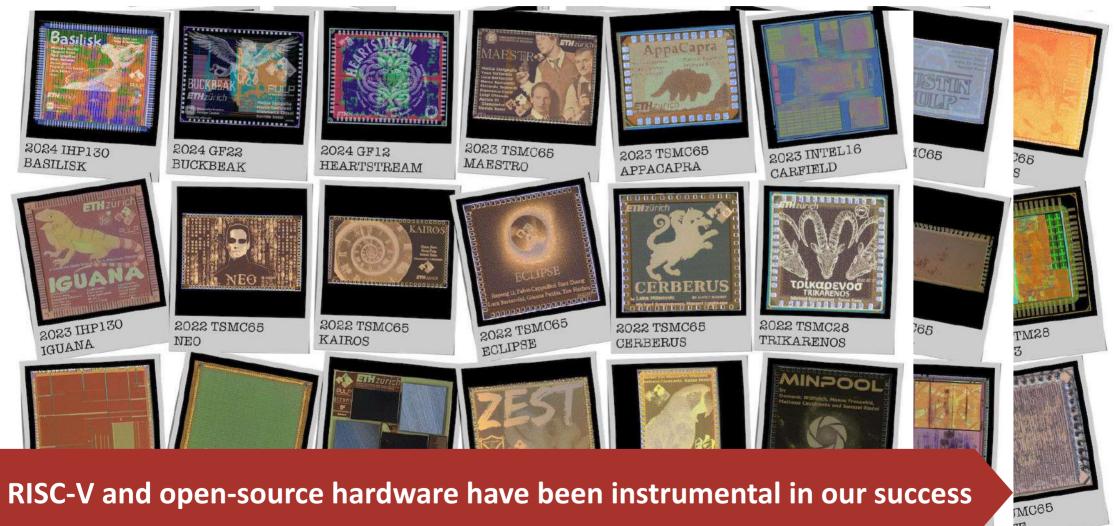

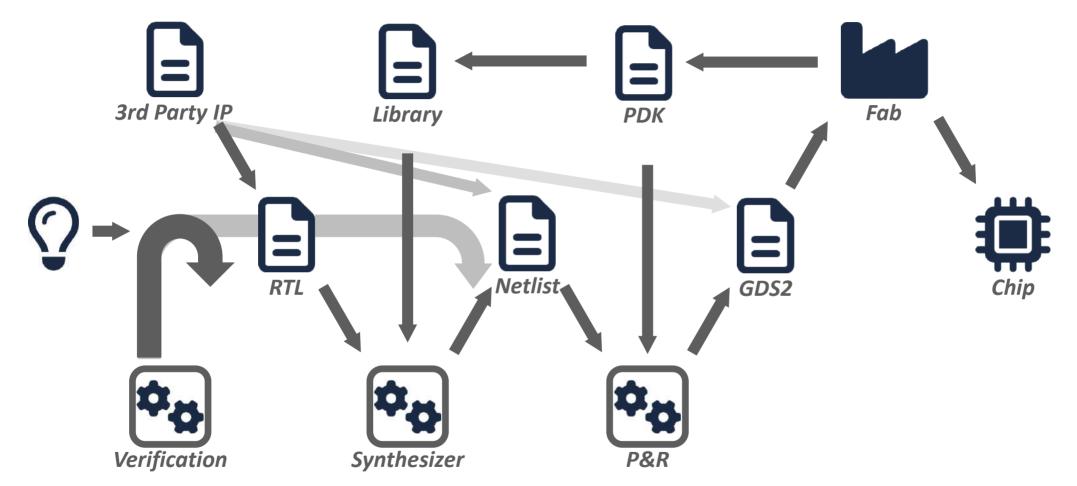

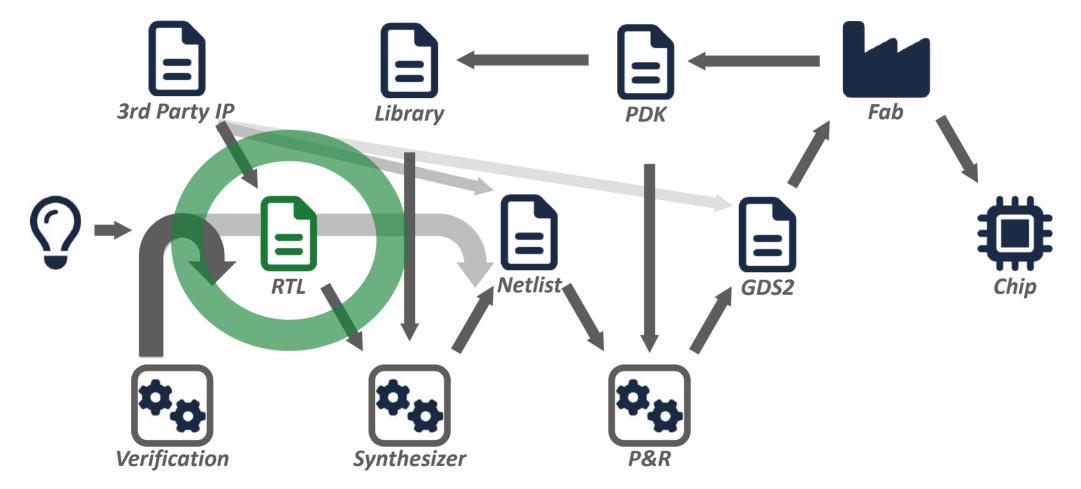

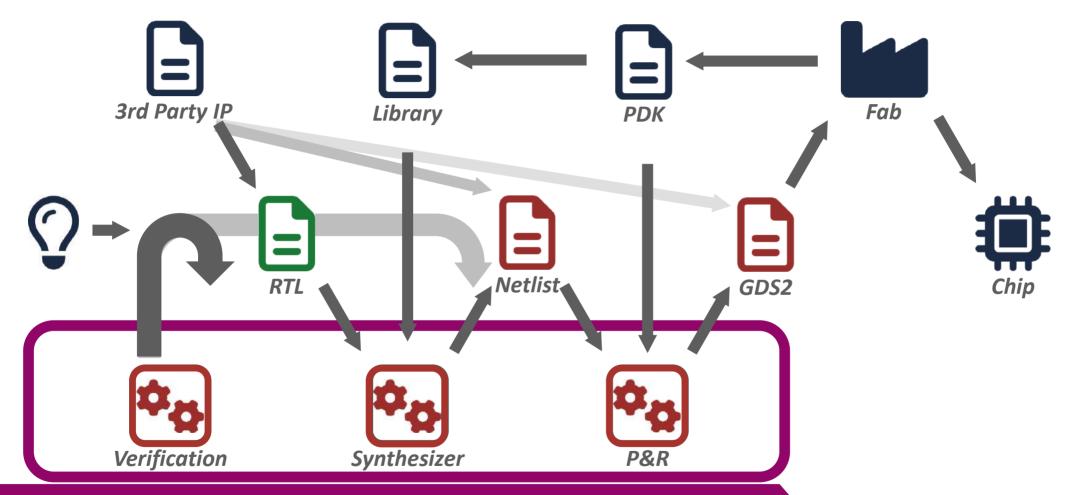

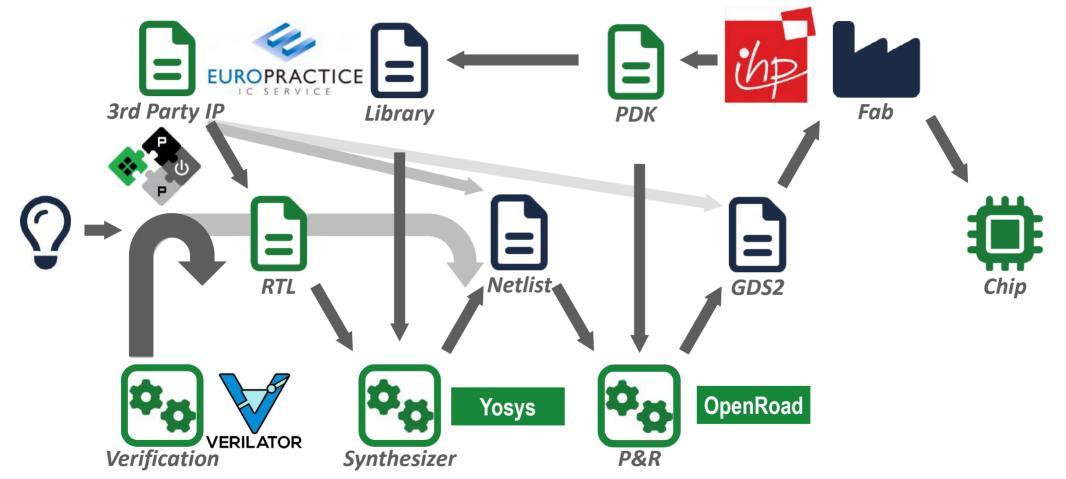

### A simplified view of the IC design flow

### Р U

### Most of open source hardware is at RTL level

### We have created a sandbox to design System on Chips

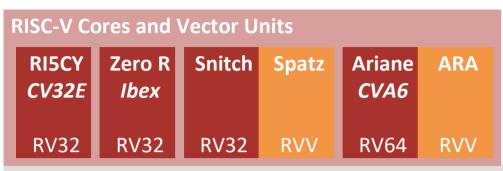

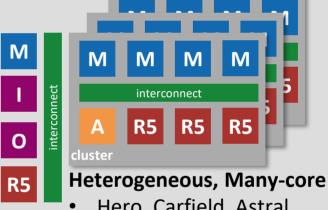

#### Single core

- PULPino, PULPissimo

- Cheshire

- OpenPULP

- **ControlPULP**

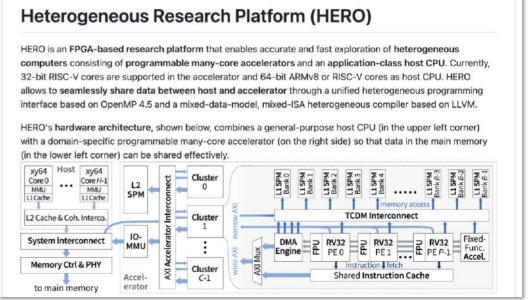

- Hero, Carfield, Astral

- Occamy, Mempool

#### **Accelerators and ISA extensions**

XpulpNN, **XpulpTNN**

ITA (Transformers) **RBE, NEUREKA** (QNNs)

**FFT** (DSP)

**REDMULE** (FP-Tensor)

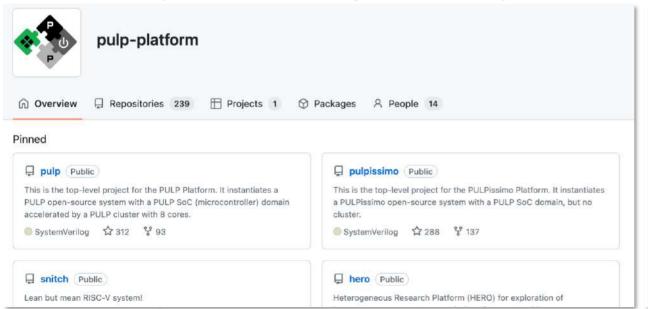

### We make everything (we can) available openly

- All our development is on GitHub using a permissive license

- HDL source code, testbenches, software development kit, virtual platform

#### https://github.com/pulp-platform

Allows anyone to use, change, and make products without restrictions.

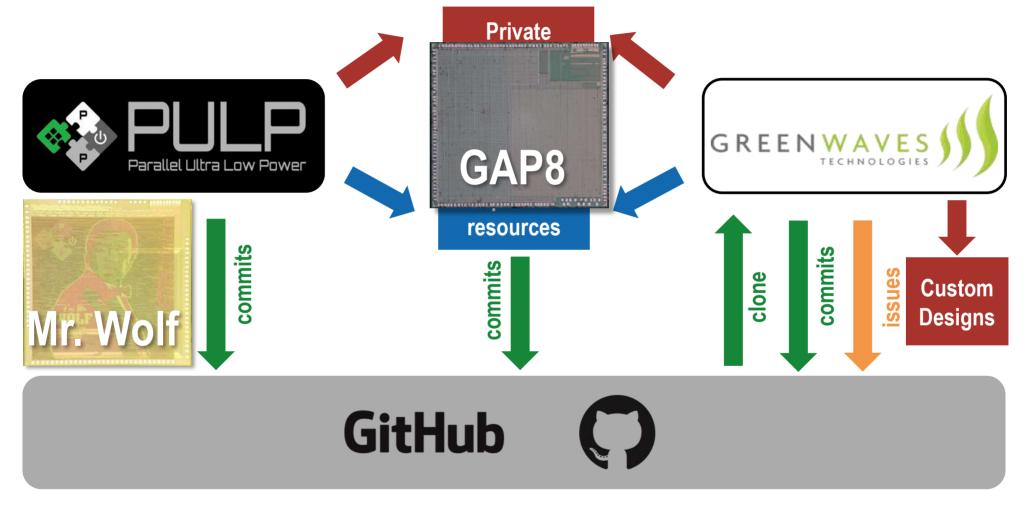

### Meet Mr. Wolf (2017) in TSMC40

- Very successful IoT processor

- 8+1 RISC-V cores

- Power converter IP from Dolphin

Win (PULP): get to use professional IP in our chips astry relevant design

• KILIOI the entire SoC openly available

Win (Dolphin): demonstrate their IP on a SoA design

- Design formed the basis of GAP8/9

- By Greenwaves Technologies

Win (Greenwaves): SoC template that can be easily productized

### How does PULP collaborate with 3<sup>rd</sup> parties?

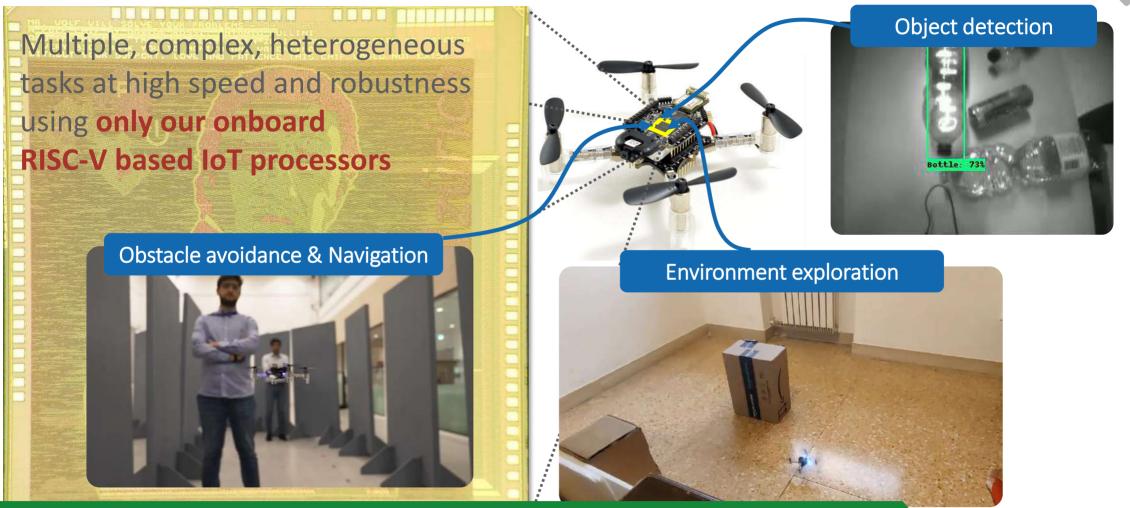

### Designs derived from Mr. Wolf powered our nano-drones

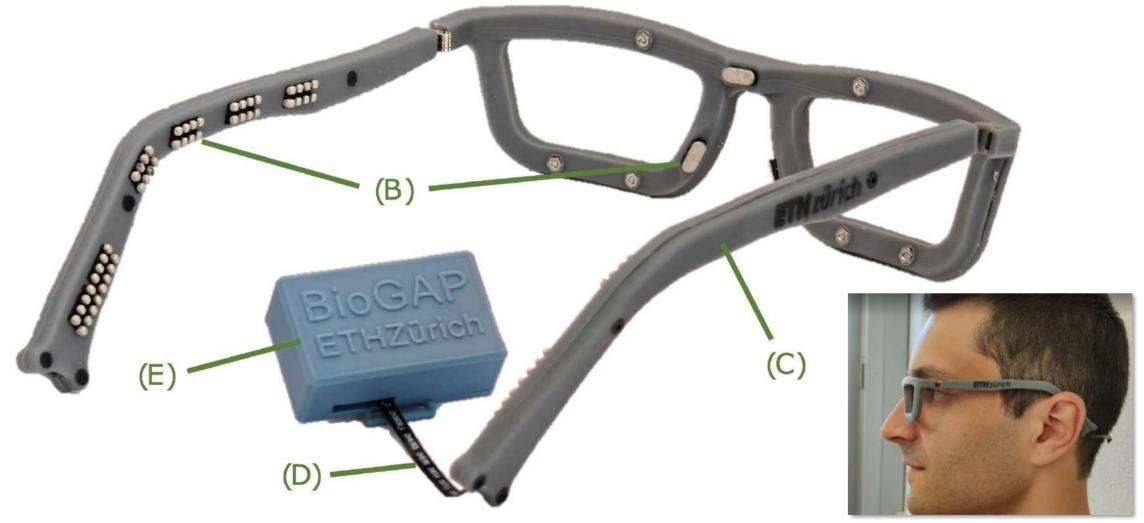

### As well as our bio-signal acquisition systems

### In the last 20 years IC Design has changed a lot

80 MGE

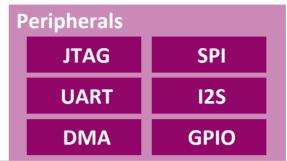

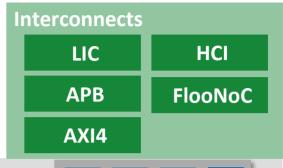

### There is so much that makes up a modern SoC

User-Space Software

Kernel-Space Software

**Hardware**

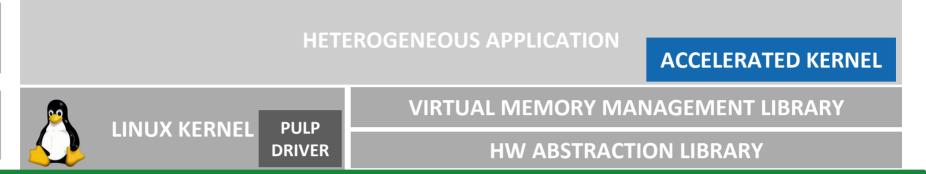

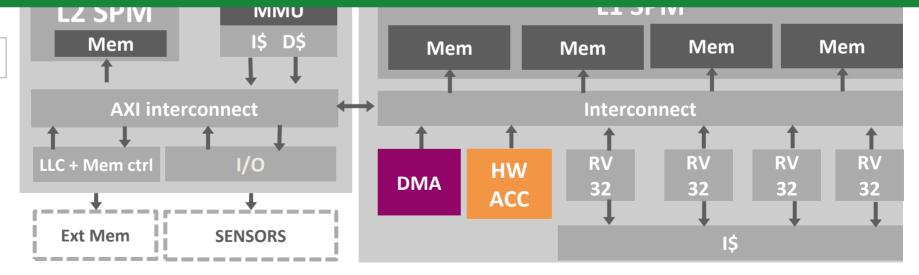

HETEROGENEOUS APPLICATION

ACCELERATED KERNEL

VIRTUAL MEMORY MANAGEMENT LIBRARY

HW ABSTRACTION LIBRARY

HOST DOMAIN RISC-V core **PULP CLUSTER** L1 SPM L2 SPM MMU I\$ D\$ Mem Mem Mem Mem Mem **AXI** interconnect Interconnect RV RV 1/0 RV LLC + Mem ctrl HW **DMA** 32 32 32 32 ACC **Ext Mem SENSORS** IŚ

### In a typical design, innovation is only in a limited scope

Kernel-Space Software

#### Open-source silicon-proven SoC template helps concentrate work where it counts

Hardware

### Diverse set of open source based industry collaborations

GF22 (2018)

#### **Arnold**

eFPGA coupled with a RISC-V microcontroller.

In one year from agreement to actual tapeout

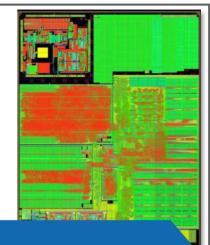

GF22 (2022)

#### Marsellus

Heterogeneous IoT processor With Aggressive voltage scaling

**DILIPHIN**

#### Permissive open-source licensing key to our industrial relationships

#### Siracusa

SoC for Extended Reality visual processing

### Carfield

Open-Research platform for safety, resilient and time-predictable systems

### And many continue to use our work for their research

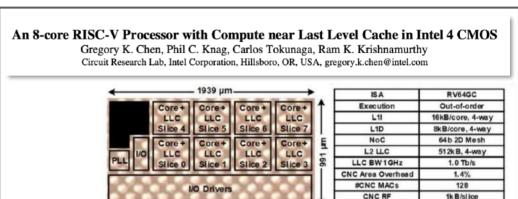

intel

VLSI Symposium 2022

#### AutoDMP: Automated DREAMPlace-based Macro Placement

Anthony Agnesina aagnesina@nvidia.com NVIDIA Corporation Austin, TX, USA

Austin Jiao ajiao@nvidia.com NVIDIA Corporation Santa Clara, CA, USA Puranjay Rajvanshi prajvanshi@nvidia.com NVIDIA Corporation Santa Clara, CA, USA

Ben Keller benk@nvidia.com NVIDIA Corporation Santa Clara, CA, USA Tian Yang tiyang@nvidia.com NVIDIA Corporation Santa Clara, CA, USA

Energy Eff. 0.6V

LLC Energy Eff. 0.6V

Brucek Khailany bkhailany@nvidia.com NVIDIA Corporation Austin, TX, USA Geraldo Pradipta gpradipta@nvidia.com NVIDIA Corporation Santa Clara, CA, USA

285 GOPS/W

1.6 TOPS/W

Haoxing Ren haoxingr@nvidia.com NVIDIA Corporation Austin, TX, USA

#### Some smaller companies you might have heard of @

ISSCC Keynote 2020 — Nature 2020

B to 20 ab 4b

Tearing time (s)

Fig. 4) Converging plans and rise MEC VCPU. Harmonic conditioning pinks and all memorated horself fine desiring agreed called policy services.

For allocked Avience BICK VCPU.

Figure 7: Pre-CTS placements of the logical groups and cell densities of the MemPool Group designs using NanGate 45nm process (freq. - 333 MHz, density - 68%). Congestion (HV): Innovus (2.66%/1.54%). AutoDMP (3.48%/1.186%).

ISPD'23

## Unlocking the rest of the design flow: Open PDK and EDA

## The output (and even scripts) of EDA vendors are closed

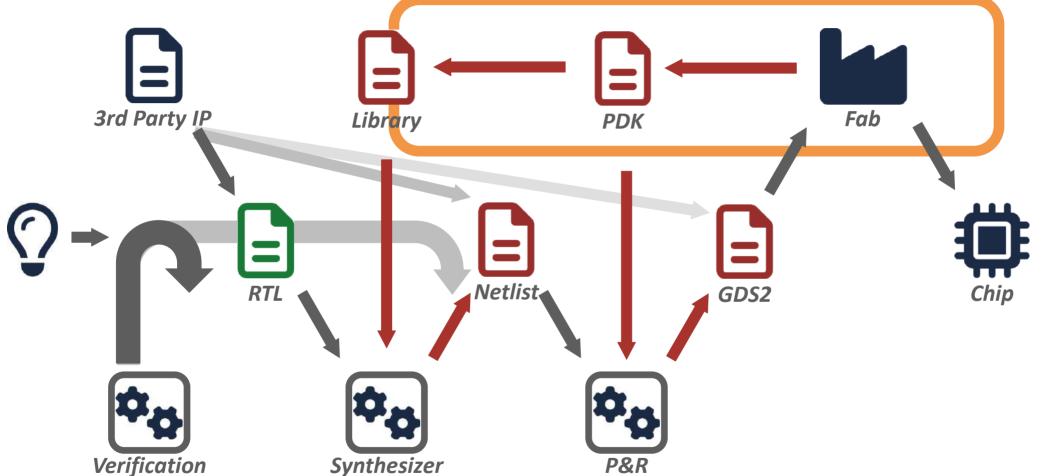

### The chip will contain information from the PDK of the Fab

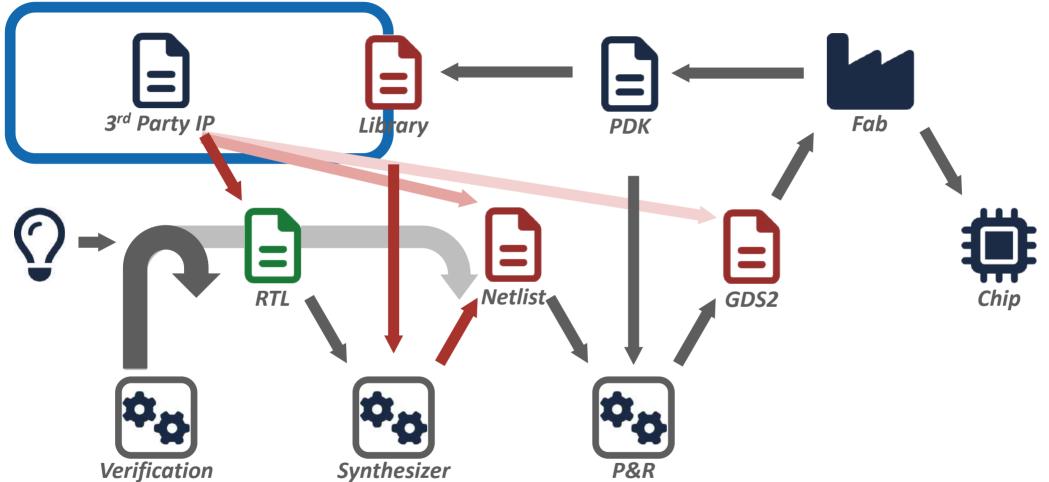

### Most designs will include some 3<sup>rd</sup> party IP

## We need openness along the whole chain: RTL, EDA, PDK

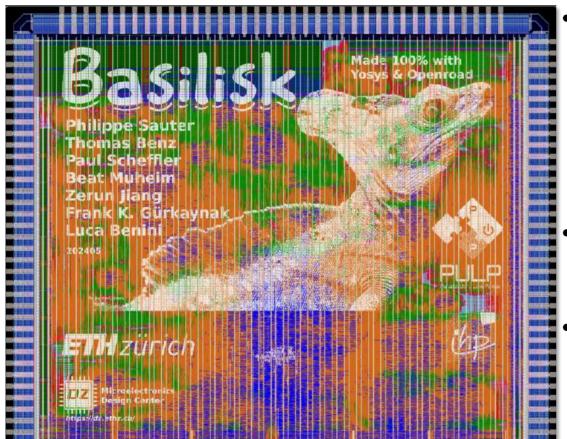

### Meet Basilisk: Open RTL, Open EDA, Open PDK

#### **Designed in IHP 130nm OpenPDK**

- 6.25mm x 5.50mm

- 60MHz

- 1.08 MGE logic, 60% density

- 24 SRAM macros (114 KiB)

#### CVA6 based SoC

- Runs and boots Linux

- **Active collaboration with**

**YosysHQ**

Open-source EDA tools already enable complex designs, it will only get better

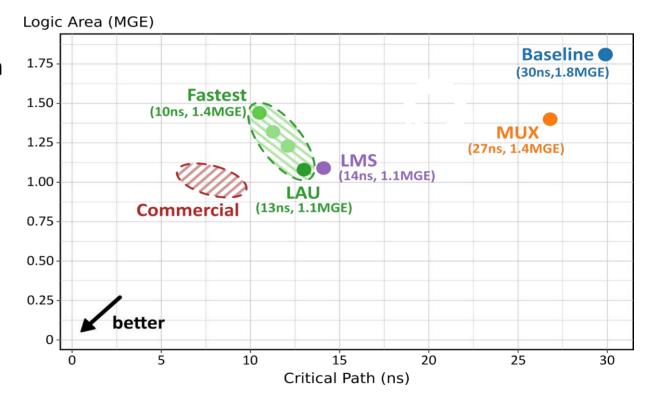

### Working with open-source EDA groups to close the gap!

#### Basilisk is the first end-to-end open-source Linux-capable RV64 SoC

- DRAM interface & rich IO (USB 1.1, VGA, SPI, ...)

- Silicon-proven, configurable, MGE-scale design

#### Improved FOSS EDA flow

- SV-to-Verilog chain @ <2min runtime</li>

- Yosys synthesis:

- $\rightarrow$  1.1 MGE (1.6×) @ 77 MHz (2.3×)

- → 2.5× less runtime, 2.9× less peak RAM

- OpenROAD P&R: tuning

- → -12% die area, +10% core utilization

### github.com/pulp-platform/cheshire-ihp130-o

### Benefits of end to end openness

Research

- Easier collaboration (no NDAs)

- Reproducible results, benchmarking

- Combined impact of design and design automation

**Education**

- Increased accessibility

- No black boxes, full visibility

- Experiment with flows and tools

**Industry**

- Transparent chain of trust, sovereignty

- Lower initial cost

- Faster research → product

### Our open source principles support funded projects

# TAICHIP

European Processor Initiative

TRISTAN

Successful partnerships with both industry and academia

CONVOLVE

### Final words

- We use open source because it works

- Allows us to manage complex designs

- Facilitates Industry/Academia Relationships

- Creates Auditable Designs, Reproducible Results

Helps us and others concentrate work where it matters

- Open Source sees no borders

- There is no 'European/Chinese/American Open Source',

- There can be 'European/Chinese/American support for Open Source'

Open Source is global, it just can have more or less support in a region/country