UNIVERSITÀ DI BOLOGNA

### End-to-end open-source IC design

Digital Circuits and Systems Group and the PULP team

Frank K. Gürkaynak kgf@iis.ee.ethz.ch

**PULP Platform** Open Source Hardware, the way it should be!

### PULP team at ETH Zürich: Open-source HW since 2013

**ETH** zürich

- Led by Luca Benini

- Professor at ETH Zürich and University of Bologna

- Large team of around 100 people

- Parallel Ultra Low Power (PULP) platform

- <u>https://pulp-platform.org/</u>

- <u>https://x.com/pulp\_platform</u>

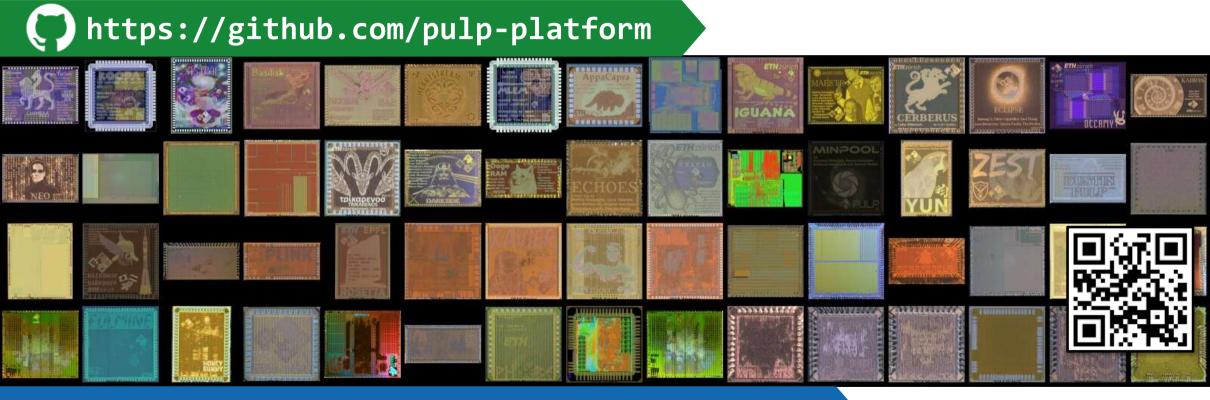

### We have designed over 60 ASICs using open-source HW

#### All our designs are based on open-source HW published on our GitHub page

• All using a permissive open source license (SolderPad)

#### See our chip gallery under: http://asic.ethz.ch/

ALMA MATER STUDIORU UNIVERSITÀ DI BOLOGN

End-to-end open-source IC Design - Frank K. Gürkaynak

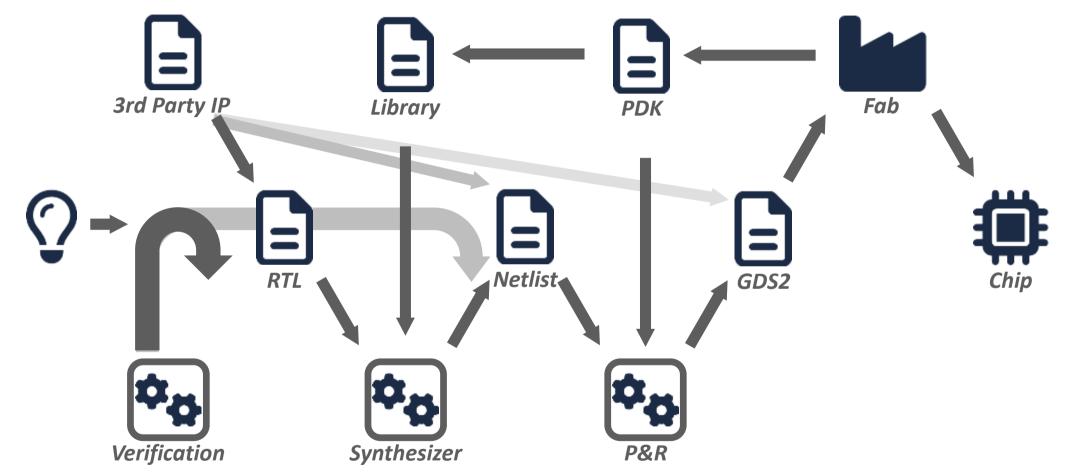

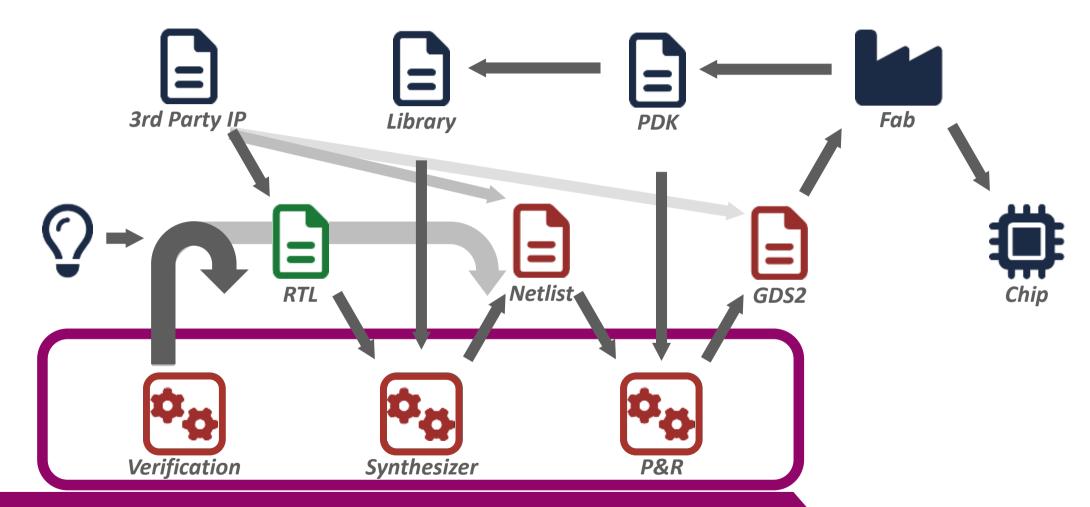

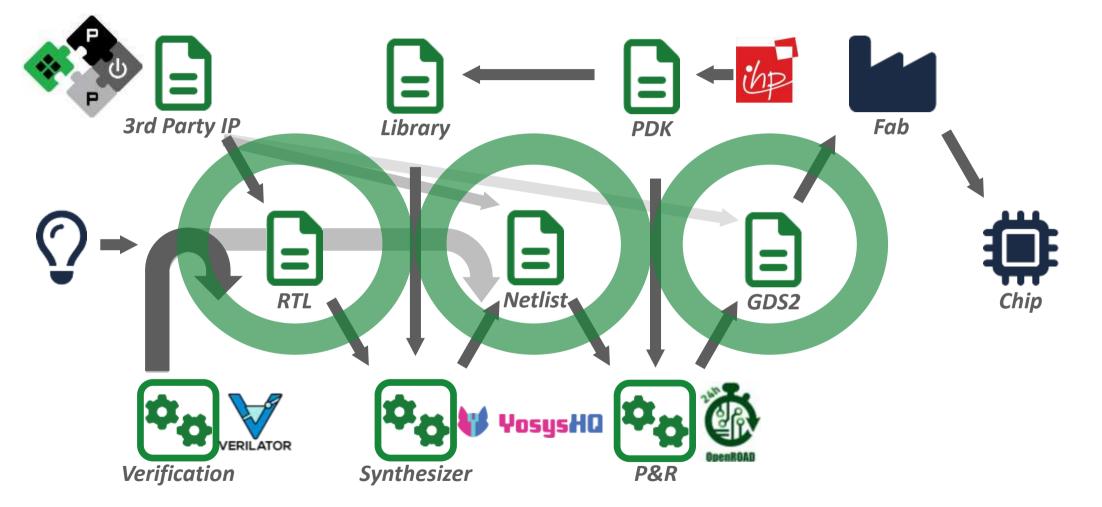

### Simplified IC design flow

End-to-end open-source IC Design - Frank K. Gürkaynak

4

2025 VLSI

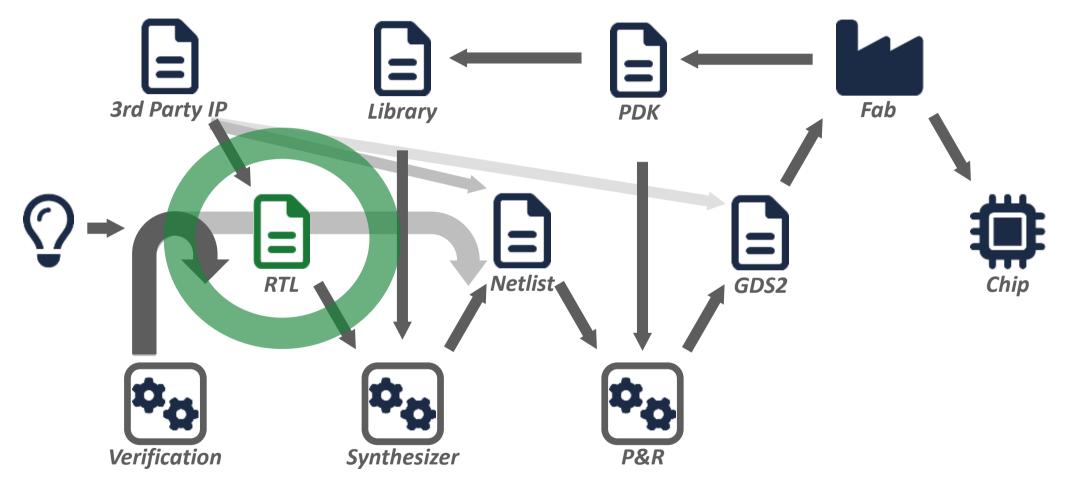

# Simplified IC design flow: at the moment only RTL

End-to-end open-source IC Design - Frank K. Gürkaynak

5

2025 VLSI

### Simplified IC design flow: proprietary tools

#### **EDA vendors limit the output of their tools**

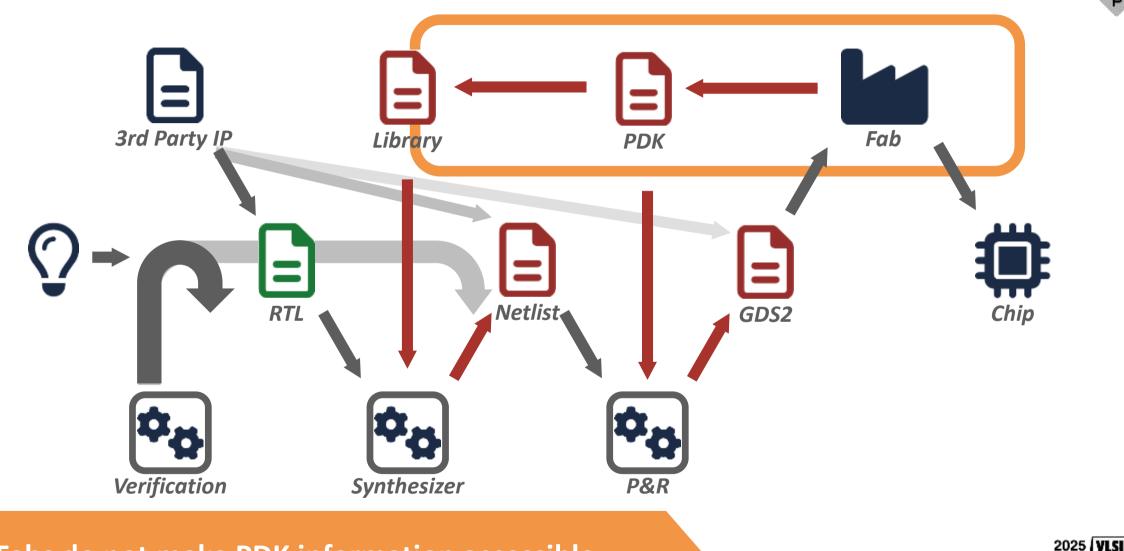

### Simplified IC design flow: technology provider

Fabs do not make PDK information accessible

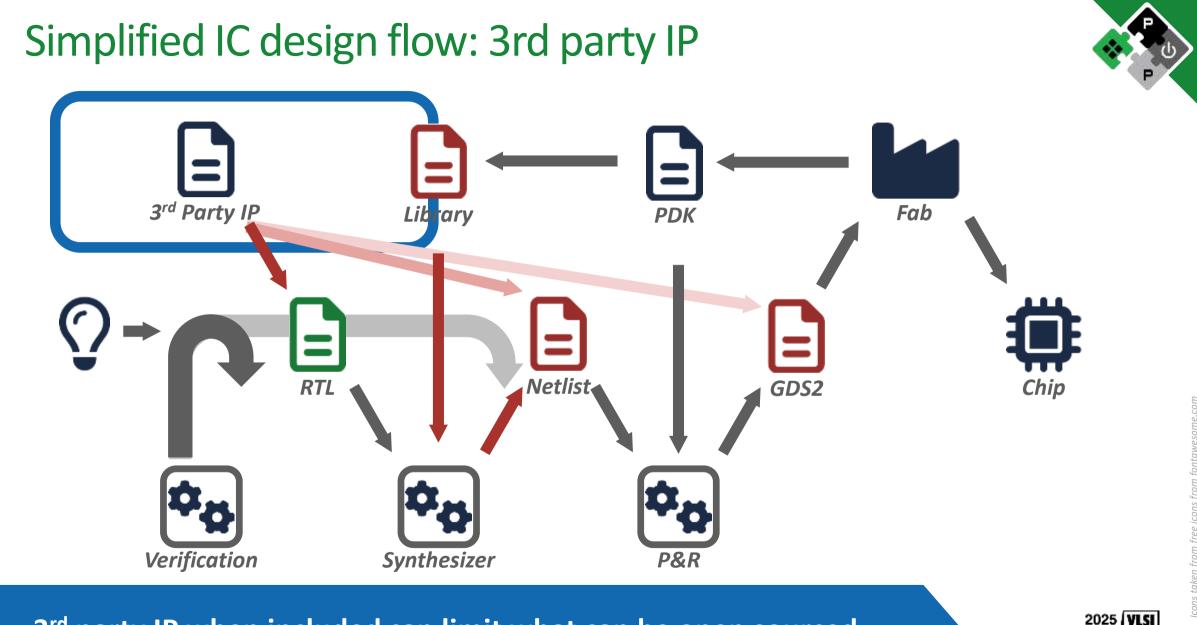

3<sup>rd</sup> party IP when included can limit what can be open sourced

8

### Physical Design (may have dependencies to technology information)

#### Tools (EDA)

**ETH** zürich

- Front-end tools (Synthesis)

- Back-end tools (Placement and Routing)

- Verification tools (Simulation)

#### Manufacturing (PDK)

- Design rules for manufacturing (separation, minimum width of metals)

- Layer stack information for parasitics (thickness, dielectric constants..)

- Device models (SPICE parameters) for simulation

### And I want to talk about why I believe end-to-end open flows are important

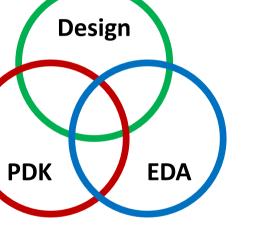

# End-to-end open-flow aims to open all steps of IC design

#### Design

- RTL / HDL descriptions (quite common)

- Schematics / Physical Design (may have dependencies to technology information)

# Notice that open parts in IC flow are independent

It is possible to use open design with closed EDA and closed PDK (Picobello, Flamingo)

Or have open designs using open EDA on a closed PDK (SeyrITA)

As well as having open designs using commercial EDA with open PDKs (EZ Library)

ETH zürich

But end goal is to allow open designs using open EDA and open PDKs (Basilisk, Mlem, Koopa)

Of course combinations with closed designs are also possible, but these do not interest me so much  $\Im$

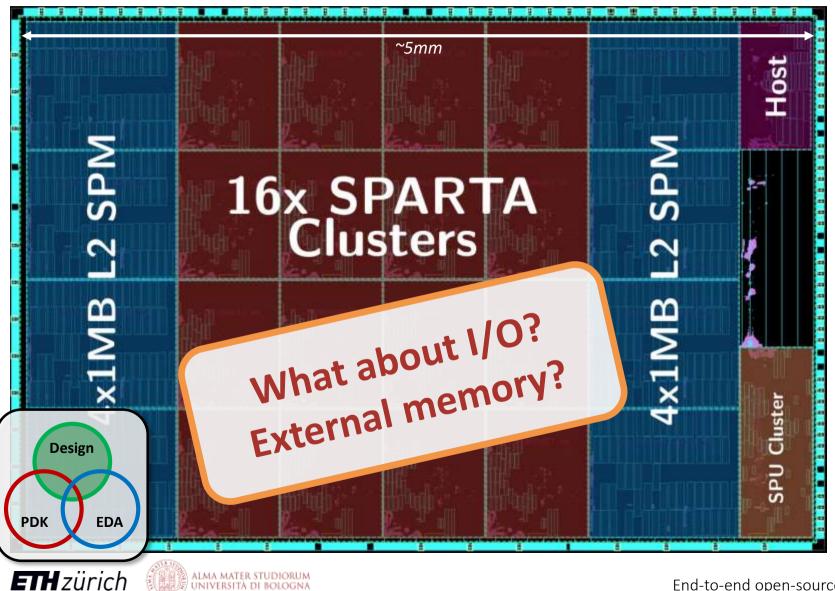

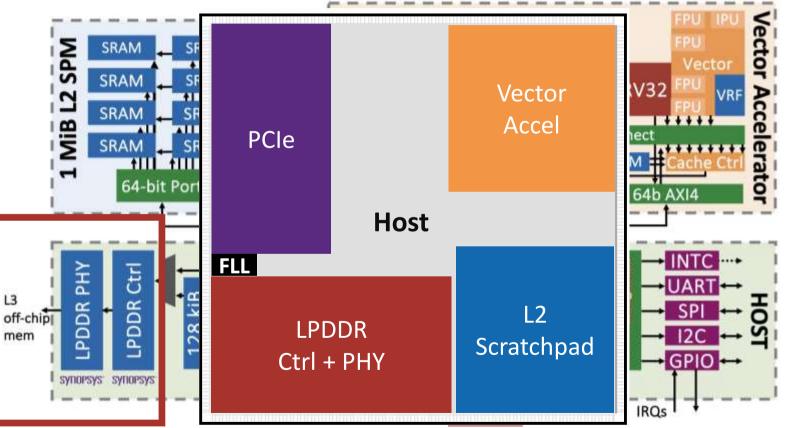

### Here is Picobello: our latest design in TSMC 7nm

- 8x 1MB of on-chip L2

- Linux capable CVA6 Host

- Peripherals (JTAG, SPI, I2C)

- Running at 1+ GHz (WC),

> 256 GFLOP/s (FP64)

> 2 TFLOP/s (FP8)

- Tape-out August 2025

EUPI

• Part of the EU Pilot project

11

2025 VLSI

### You need help to make large modern SoCs

- There are many innovative parts in Picobello

- Hopefully you will read about it in publications starting in 2026

- But you can not afford to design all parts of an SoC from scratch by yourself

- It builds on successful designs from the past

- CVA6 core •

- Cheshire platform & peripherals

- Snitch clusters •

- FlooNoc •

- AXI •

- Needs collaborations with experienced teams

- University of Bologna, TU-Munich

#### What about technology specific IPs? DDR, PCIe?

- : https://github.com/openhwgroup/cva6

- :https://github.com/pulp-platform/cheshire

- :https://github.com/pulp-platform/snitch\_cluster

- :https://github.com/pulp-platform/floonoc

- :https://github.com/pulp-platform/axi

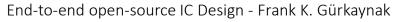

# Finding such IP is not easy, you need great partners

**Meet Flamingo**

**ETH** zürich

SoC with Vector based accelerator for AI applications in GF22

We would like to emphasize that this floorplan is not drawn to scale

- **GlobalFoundries**<sup>®</sup>

- **EDA support by SYNOPSYS**

- **Interface IP** DDR / PCIe by **SYNOPSYS**<sup>®</sup>

# Finding such IP is not easy, you need great partners

- **Meet Flamingo**

- SoC with Vector based accelerator for AI applications in GF22

### Sharing our FLL with others that need it

- When you start designing in more modern technologies clock rates increase

- For 28nm and less clock rates of 500MHz 2GHz are easily possible

- It is difficult to bring such clocks externally, an internal clock generator could help

- Good luck getting access to a low-cost clocking IP  $\bigcirc$

- We designed an FLL (Frequency Locked Loop) back in 2016

- D. E. Bellasi and L. Benini, "Smart Energy-Efficient Clock Synthesizer for Duty-Cycled Sensor SoCs in 65 nm/28nm CMOS," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 9, pp. 2322-2333, Sept. 2017, doi: 10.1109/TCSI.2017.2694322.

- Ported and taped-out in many technologies: UMC65, TSCM65, GF22, GF12, TSMC7...

People have asked us repeatedly if we could share our FLL

### .. and we really want to share our FLL, we know how much it helped us

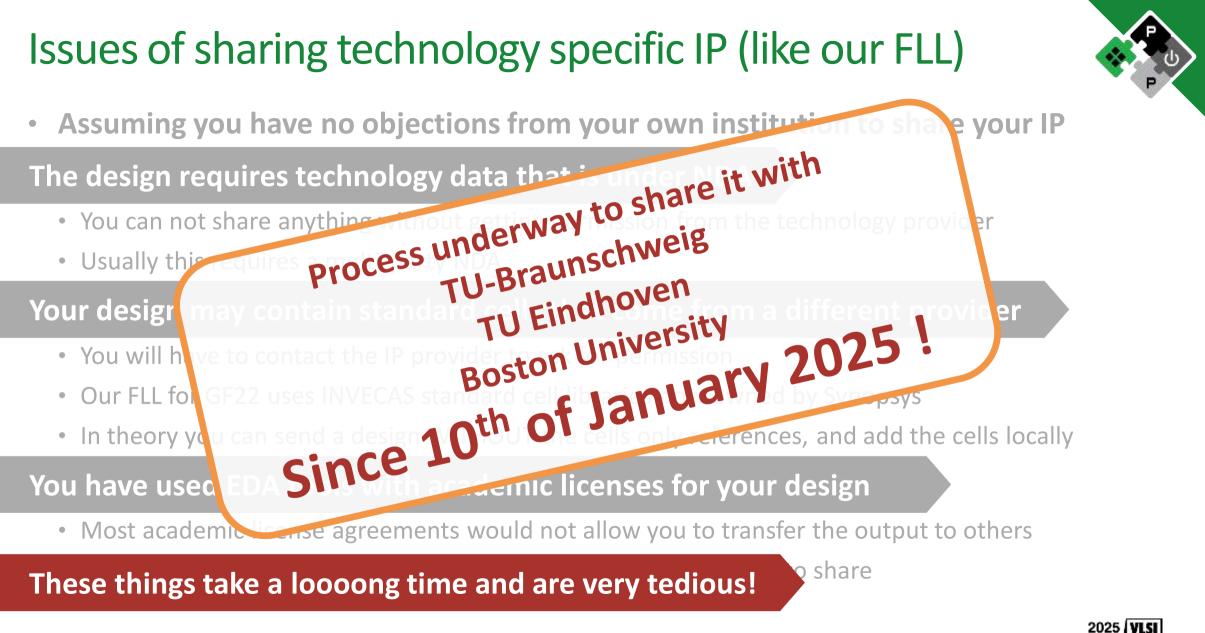

### Issues of sharing technology specific IP (like our FLL)

Assuming you have no objections from your own institution to share your IP

#### The design requires technology data that is under NDA

- You can not share anything without getting permission from the technology provider

- Usually this requires a multi-party NDA

Your design may contain standard cells that come from a different provider

- You will have to contact the IP provider to ask for permission

- Our FLL for GF22 uses INVECAS standard cell libraries now owned by Synopsys

- In theory you can send a design WITHOUT the cells only references, and add the cells locally

#### You have used EDA tools with academic licenses for your design

- Most academic license agreements would not allow you to transfer the output to others

- You need to contact the EDA vendor and ask for their permission to share

End-to-end open-source IC Design - Frank K. Gürkaynak

17

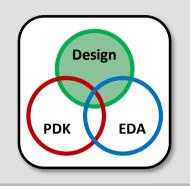

## End-to-end Open-Source flow would help share IP

End-to-end open-source IC Design - Frank K. Gürkaynak

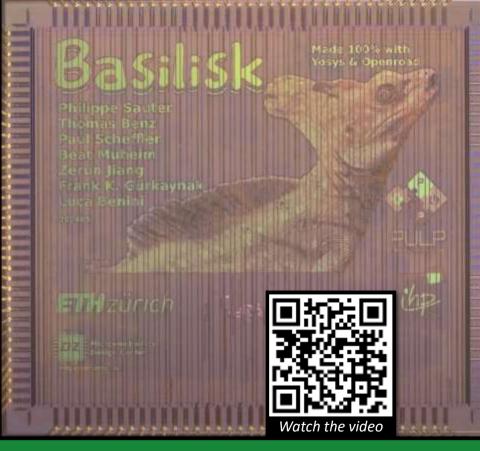

### Meet Basilisk: End-to-end open SoC booting Linux

#### **Booting Linux on**

# Basilisk

Design

EDA

PDK

**ETH** zürich

an end-to-end open-source 64-bit RISC-V SoC in IHP 130nm BiCMOS

ürich

### **Open Design**

Cheshire with CVA6

### **Open EDA**

- Yosys (with -slang)

- OpenROAD

- KiCAD (for board)

### **Open PDK**

- IHP 130

- Open standard cells

- Memory macros •

### github.com/pulp-platform/cheshire-ihp130-o

#### End-to-end open-source IC Design - Frank K. Gürkaynak

####

2025 VLSI

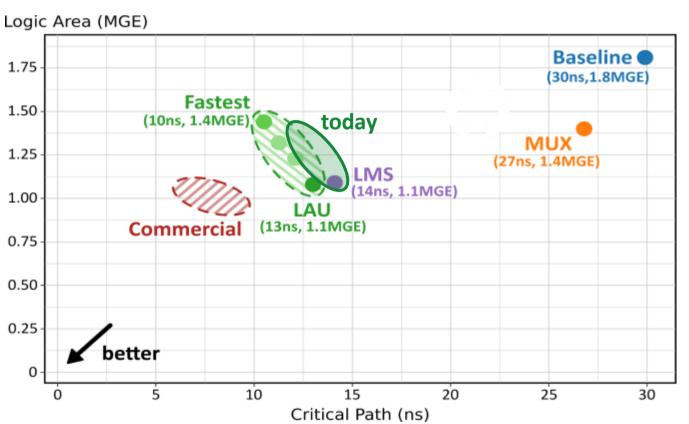

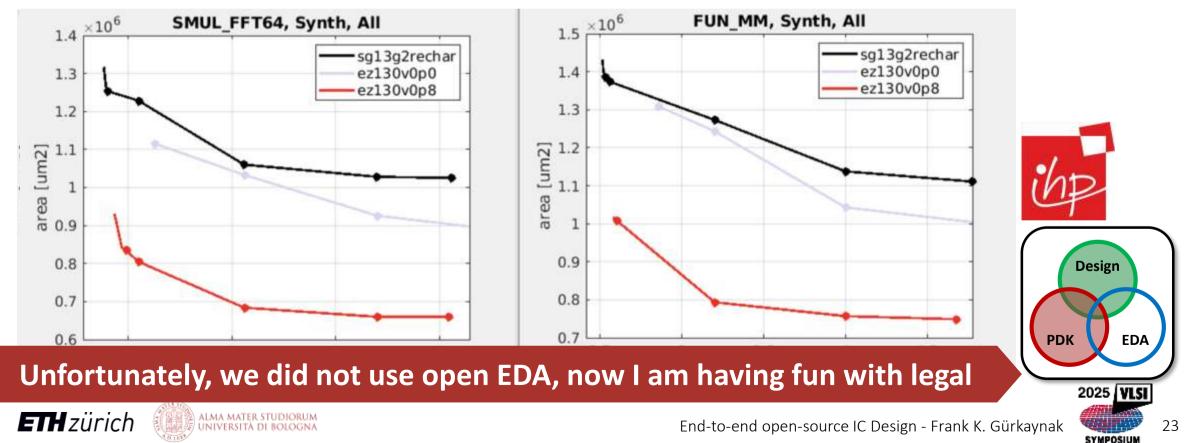

# Working with open-source EDA groups to close the gap!

There is still a gap to commercial tools, but it is much less than you think it is

- Improvements until June 2024

- SV-to-Verilog chain @ <2min runtime

- Yosys synthesis:

**ETH** zürich

- $\rightarrow$  1.1 MGE (1.6×) @ 77 MHz (2.3×)

- $\rightarrow$  1.4× less runtime, 2.4× less peak RAM

- OpenROAD P&R: tuning

- $\rightarrow$  -12% die area, +10% core utilization

- Improvements June-October

- Yosys-slang replaces SV2V

- 1.6× less runtime, 10× less peak RAM <sup>o</sup>

- -10% logic area (preliminary)

## At ETH Zürich, IC Design teaching uses open source HW

P 0

- Starting 2025, our IC Design course switched to (mostly) open source

- Using IHP 130, Yosys and OpenROAD

- Parts for backannotated simulation, test pattern generation, DRC/LVS, still use proprietary tools

- Exercises based on a 32bit RISC-V microcontroller we call Croc

### https://github.com/pulp-platform/croc

- Project based grading

- Students (in groups of two) will have to modify the exercise design

- Best five designs will be taped-out

- Huge advantage:

- We can share lecture and exercise content with everyone

### https://vlsi.ethz.ch

### Reliable collection of open source tools is essential!

- Most open source developers have their own idea about the environment

- Getting several independent tools to work at the same time is very demanding work

- Preparing/sharing lectures require you to be able to point to a reliable image

### https://github.com/iic-jku/IIC-OSIC-TOOLS to the rescue

| README Apache-2.0 license                                                                                                                                                                                                                                                                                                                                                                                                                  | E                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| IIC-OSIC-TOOLS                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

| DOI 10.5281/zenodo.15044726                                                                                                                                                                                                                                                                                                                                                                                                                |                        |

| This environment is based on the efabless.com FOSS-ASIC-TOOLS.                                                                                                                                                                                                                                                                                                                                                                             |                        |

| <b>IIC-OSIC-TOOLS</b> (Integrated Infrastructure for Collaborative Open Source IC Tools) is an all-in-oc<br>container for open-source-based integrated circuit designs for analog and digital circuit flows. T<br>architectures x86_64/amd64 and aarch64/arm64 are natively supported based on Ubuntu 24.04<br>release 2025.01). This collection of tools is curated by the Department for Integrated Circuits<br>Kepler University (JKU). | he CPU<br>4 LTS (since |

Thanks Harald 🙂

### EZ Library: new standard cells for IHP130

- VLSI 5 lecture by the Integrated Information Processing group at ETH Zürich

- By Oscar Castañeda Fernández, Christoph Studer and a bit of support from me

- In one semester, 18 students re-designed a standard cell library for IHP130

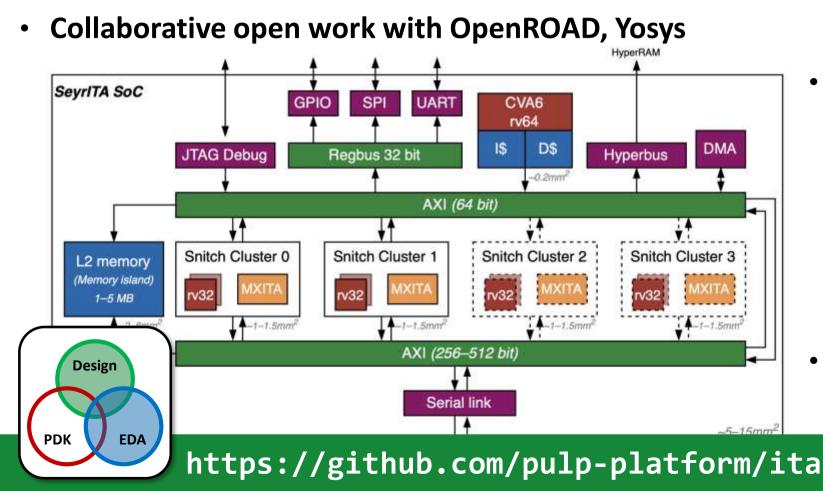

### SeyrITA, our most ambitious project for embodied AI

- Designing a research relevant SoC using open source EDA in GF22

- State of the art accelerator for embodied AI, using Integer Transformer Accelerator (ITA)

# GlobalFoundries"

- Challenging work

- Large design, modern technology

- We encounter problems daily

- We try to solve them one problem at a time

- Confident we will get it done

- Target tape-out

- End of 2025 / Early 2026

gn - Frank K. Gürkaynak

### There are still many challenges, our work is not done!

- We need more open PDKs

- Something in the 65nm 28nm range would be a game changer

- Drafted an open letter to raise awareness with 300+ signatures

https://open-source-chips.eu/

- Parts of open EDA already in good shape, but there are gaps

- Many independent groups are working on tools, need to support inter-operability

- Possible EU funding for 20MEUR for open source EDA development, project outline submitted

- Opportunity to go beyond what standard tools are able to deliver, close the PPA gap!

- End-to-end open source design requires set of IPs that others can use

- Memories, Serial I/O, Data converters, Memory controllers, PHYs for common protocols

- List is long, we will have enough work to do ☺

#### End-to-end Open-Source IC Design is already working! It will only get better **Easier collaboration / sharing Open reproducible results** Need to stand on the shoulder of giants Everyone can verify performance claims Share common parts that all need • Allows us to generate example datasets that can be used to train/improve tools Concentrate work/time where it matters Innovation all over IC Design Accessible teaching for all Share courses, designs, examples No longer limited to only design Create tutorials, knowledge bases Improve design flows, design tools Lower entry barriers also for industry Create new opportunities

26

2025 VLS