Introduction

This page shortly summarizes PULP implementation. For a detailed overview of PULP within the RISC-V ecosystem see the dedicated GitHub page maintained by Ahmad Mirsalari.

Processors

RISC-V compatible cores written in SystemVerilog

| Processor | Bits/Stages | Description |

|---|---|---|

| CV32E40P (RI5CY) |

32bit / 4-stage |

Our workhorse 4-stage core that implements, the RV32-IMC, has an optional 32-bit FPU supporting the F extension and instruction set extensions for DSP operations, including hardware loops, SIMD extensions, bit manipulation and post-increment instructions. |

| Ibex (Zero-riscy) | 32bit / 2-stage |

An area-optimized 2-stage 32-bit core for control applications implementing RV32-IMC. |

| Micro-riscy | 32bit / 2-stage |

A minimal area 2-stage 32-bit core with 16 registers and no hardware multiplier implementing RV32-EC. |

| CVA6 (Ariane) | 64bit / 6-stage |

A 6-stage, single issue, in-order 64-bit CPU which fully implements I, M, C and D extensions as specified in Volume I: User-Level ISA V 2.1 as well as the draft privilege extension 1.10. It implements three privilege levels M, S, U to fully support a Unix-like (Linux, BSD, etc.) operating system. It has configurable size, separate TLBs, a hardware PTW and branch-prediction (branch target buffer, branch history table and a return address stack). The primary design goal was on reducing critical path length to about 20 gate delays. |

| Snitch | 32bit / 1-stage |

A single-stage, single-issue 32-bit RISC-V integer core tuned for high energy efficiency. It aims at maximizing the compute/control ratio by making the FPU external to the core and the dominant part of the design, as well as mitigating the effects of deep pipelines and dynamic scheduling. |

Peripherals

It would be difficult to build a system without the help of peripherals. We have developed customized accelerators, AXI compatible interconnect solutions, different DMA engines and various peripherals to communicate with the environment including GPIO, SPI, I2S, JTAG and many more.

Microcontrollers

The simplest PULP based systems are our micro-controllers that can be configured to use any 32-bit RISC-V cores we have developed (RI5CY, Zero-riscy, Micro-riscy) add memory and some peripherals. Advanced versions also allow Accelerators to be added to the system.

| Microcontroller | Description |

|---|---|

| PULPino | A minimal single-core RISC-V SoC, our first open source release that has attracted a lot of attention. |

| PULPissimo | An advanced version of our microcontroller. The main change is the presence of the logarithmic interconnect between the core and the memory subsystem allowing multiple access ports. These are then used by an integrated uDMA that is able to copy data directly between peripherals and memory, as well as optional accelerators that we call Hardware Processing Engines (HWPEs). |

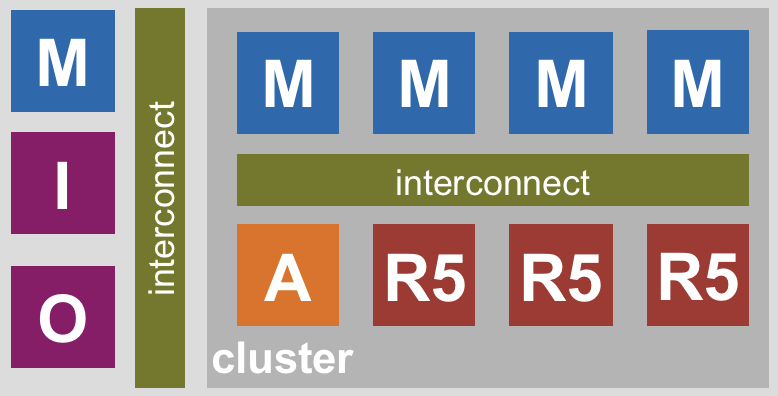

Cluster-based systems

Our more advanced systems are based on clusters of 32-bit RISC-V cores with direct access to a small and fast scratchpad memory (Tightly Coupled Data Memory). The cluster is supported by a SoC that houses a larger second level memory, peripherals for input and output, and in later versions a complete PULPissimo class microcontroller for power management and basic operations. Most of our research is based on the development of architectures based on these systems. Mia Wallace, Honey Bunny, Fulmine and finally Mr. Wolf are all such systems, and the source code for the latest system has been released as OPENPULP on our GitHub page.

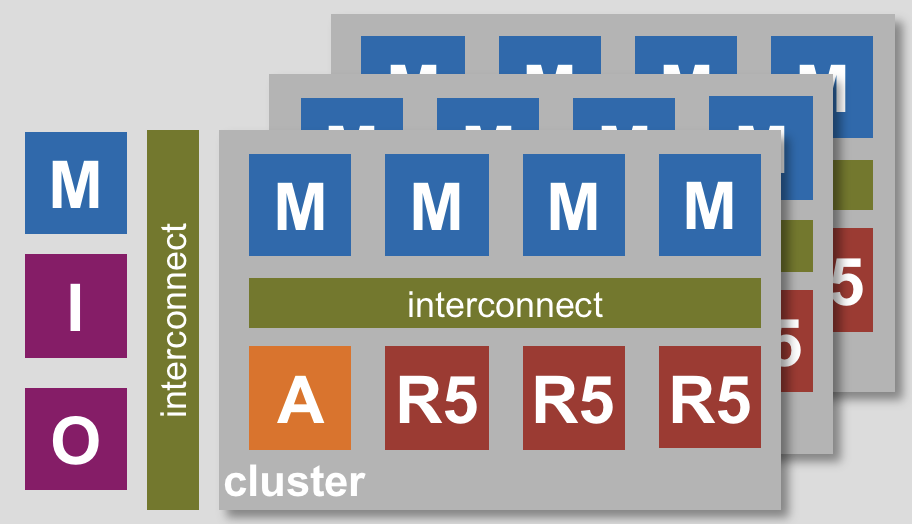

PULP as a multi-cluster accelerator

We have also expanded our work for larger workloads, where a PULP system that contains multiple clusters is connected to a regular computing node. In this scenario, the PULP cluster is used as an energy-efficient accelerator for DSP loads. Our HERO platform release is such a system.

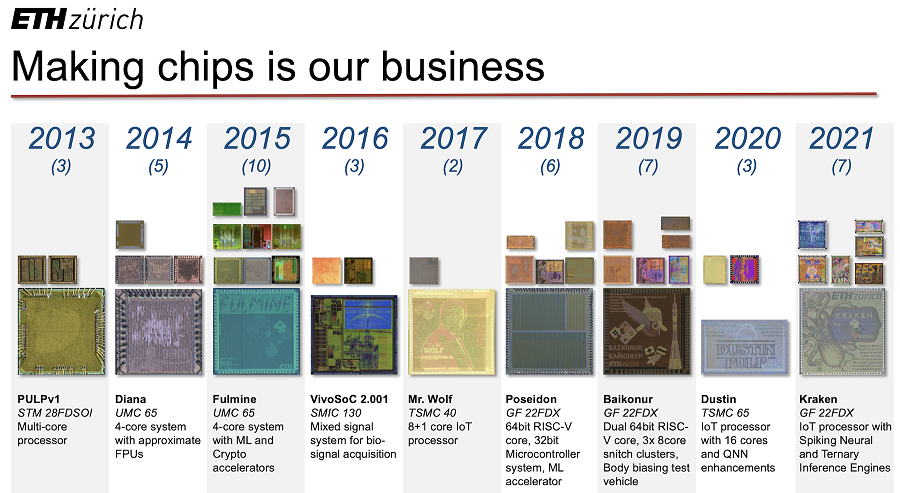

Silicon Proven designs

We have a long tradition of taping out ASICs at, ETH Zurich, just check our Chip Gallery. We have designed and tested more than 40 PULP related designs in several technologies, while current NDAs we have signed does not allow us to share the design databases, all these designs are based on the source code of the PULP systems that we have openly released.

| Intel 16 | Carfield |

| IHP 130 | Iguana, Basilisk, MLEM, Chiffre, Crocodilo, Fluffy, Koopa, Pjononcroc, River |

| GF 12 | Occamy, Heartstream, Astral |

| GF 22FDX | Poseidon, Kosmodrom, Arnold, Baikonur, Thestral, Vega, Kraken, Marsellus, Shaheen, Buckbeak, Chimera |

| STM 28FDSOI | PULP, PULPv2, PULPv3 |

| GF 28SLP | Honey Bunny |

| TSMC7 | Picobello |

| TSMC16 | Siracusa |

| TSMC28 | Trikarenos |

| TSMC40LP | Mr. Wolf |

| TSMC65 | Rosetta, Dustin, Zest, Yun, Minpool, Echoes, Dogeram, Darkside, Cerberus, Eclipse, Kairos, Neo, AppaCapra, Maestro |

| UMC65LL | Atomario, Scarabaeus, Imperio, Patronus, Mia Wallace, Phoebe, Artemis, Hecate, Selene, Diana, Billywig, Plink, Xavier, Urania |

| SMIC130/110 | VivoSoc, VivoSoC2, VivoSoC2.001, VivoSoC3, VivoSoC3.142 |

| UMC180 | Or10n, Sir10us |

| ALP180 | Manny, Sid, Diego |