Stellen Sie sich einen Computerchip wie eine moderne Stadt vor

Zeit.de

5 January 2025

The German magazine Zeit published an interview with Luca Benini about how to think about computer chips and about the factors involved in a successful chip design. You will learn about how chip design can be improved still further and about how the massive computing power of today's chips contributes to AI development. Read the full translated article here and here.

Bringing RVV to Life: Overcoming Hardware Gaps in RISC-V Development

Marek Pikuła, Samsung R&D Institute Poland

18 October 2024

Samsung R&D Instute published a blog by Marek Pikula demonstrating how our Ara chosen from within the RISC-V vibrant open-source IP core ecosystem, helps to support performance-focused RISC-V Vector (RVV) extension development. Ara is our RVV1.0 coprocessor for CVA6, a well-established, high-quality application-class RISC-V core. Read the full post here.

RISC-V based open-source designs from PULP Platform

EUROPRACTICE Activity report

31 March 2023

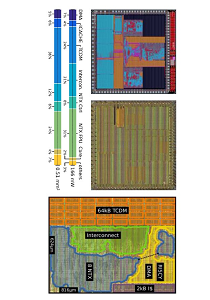

EUROPRACTICE published their Activity report for the year 2022 with PULP and ETH Zurich as part of the section "In the Spotlight". The report dedicates four pages (56 - 59) mentioning their involvement in more than 50 of our designs, among others Dogeram, Minpool, Yun, Echoes, Darkside, Zest and Marsellus. EUROPRACTICE has been an indispensable help for obtaining the licenses for the EDA design flows as well as their MPW services. We are grateful for their support. Learn more here.

Why a new generation of chips are needed for AI

Verve Ventures

12 January 2023

Verve Ventures published an interview with Luca Benini discussing the challenges of the wider adoption of AI, added benefits of edge computing such as elimination of the time required to communicate the data to a remote cloud. Next, the interview focuses on a Dutch start-up Axelera AI, its unique positioning and competition on the market and Luca's involvement in the venture as a scientific advisor. Read the entire interview here.

Meet Snitch: the Small and Agile RISC-V Processor

IEEE Spectrum

21 Oct 2021

IEEE Spectrum published an article based on an interview with Florian Zaruba focused on our Snitch. Snitch, built around RISC-V, is able to execute the majority of its basic instructions instantaneously, bypassing the need for extra, burdensome hardware. Snitch can perform most basic instructions within a single clock cycle. It was designed to execute longer latency instructions without stalling and waiting for their completion. This leads to a very compact and high-performance design compared to conventional processors that achieve high performance. Read more here.

A booting computer is as vulnerable as a newborn baby

ETH News

5 November 2019

ETH News published an interview with Luca Benini focused on the role of PULP's Ibex in the latest release of OpenTitan, the first open source silicon root of trust, initiated by Google. System hardware is increasingly the target of malicious attacks and faults go undiscovered for longer. OpenTitan checks whether the code generated by the firmware matches the expected code. Open sourcing makes the design more transparent and therefore more secure. Read more here.

ETH Zurich hebt Gleitkomma-Arithmetik auf neue Stufe

Elektroniknet.de

19 August 2019

Elektroniknet.de published an article on NTX, our Network Training Accelerator developed for floating-point arithmetic that was presented during HotChips 2019. With 260 Gflops / W, the chip implemented in 22nm FD-SOI offers unmatched energy efficiency. The primary focus is on eliminating the bottleneck common to Neumann architectures by amortizing RISC-V instructions across eight NTX units and on removing all FP load/store operations from the instruction stream through the AGUs. Read more here.

A dive into RI5CY core internals

Sam Leonard, Embecosm

13 August 2019

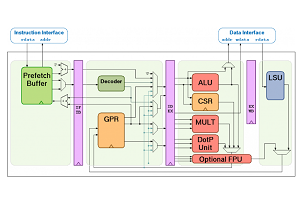

Embecosm published an article/tutorial that deals with the internals of PULP's RI5CY, our 4-stage in-order pipelined RISC-V core written in SystemVerilog that has been adopted as the first Core-V core in the OpenHW Group. The tutorial focuses on two aspects of the RI5CY implementation, the decoder and register file which need to be understood in order to make modifications that add additional instructions. Read the tutorial here.

Leveraging the Openness and Modularity of RISC-V in Space

Aerospace Research Central

5 August 2019

An article authored by Stefano Di Mascio et al. published in ARC proposes a roadmap to address present and future needs in space systems with RISC-V processors. Processors in space face unique challenges such as effects ionizing radiation and unfeasibility of direct physical maintenance. Among other aspects, the article also provides an overview of performance, area, and area efficiency for several implementations targeting microcontrollers and points that PULP's Zero-riscy reaches performance similar to that of state-of-the-art proprietary processors. Read more on ARC section Microcontrollers.

Embedded Benchmark Calls for Support

EE Times

11 June 2019

EE Times published an article on Embench, a new and free open-source alternative to the well-established suite of EEMBC benchmarks. Embench distils performance metrics from around 20 real-world applications into a single score. The effort was initiated by RISC-V pioneer David Patterson and we are proud to announce that our open-source 32-bit RISC-V core RI5CY was tentatively picked as the reference core for the benchmark. Read more here.

PULP, OpenPiton Partner on OpenPiton+Ariane Design

AB Open

5 December 2018

AB Open published an article on our PULP partnering with the The Princeton Parallel Group in order to combine the OpenPiton open-source research processor platform with our 64-bit Ariane RISC-V core. This is great news for fans of open source hardware! OpenPiton will be the go-to multicore environment for Ariane. and Ariane will have first-class upstream support in OpenPiton. Together, they will provide the ideal permissive open-source RISC-V system that scales from single-core to manycore. Read more on AB Open or on OpenPiton's website.

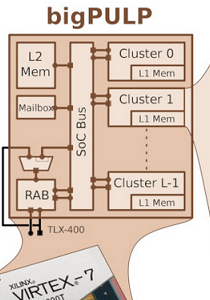

PULP Platform Announces RISC-V HERO Heterogeneous Research Platform

AB Open

19 September 2018

AB Open published an article on HERO, our open heterogeneous research platform combining an FPGA-based RISC-V many-core accelerator with an Arm Cortex-A host processor running full-stack Linux. HERO offers a complete hardware and software platform which advances accelerator programming by using the OpenMP v4.5 Accelerator Model. This enables to write a single application source file for the host and use OpenMP directives for parallelisation and accelerator offloading. Read more about HERO on AB Open or on our website.

PULP celebrates 5 years

HiPEACinfo 54

May 2018

The HIPEAC newsletter, a quarterly publication on the latest activities of the European high-performance scene, published a column on PULP celebrating 5 years of collaboration between ETH Zurich and the University of Bologna. You can find more on this topic, as well as recent updates regarding Ariane, PULPissimo and OPENPULP on page 10 of the HiPEAC Newsletter. Check out the older issues, as well. There is plenty of interesting information inside.

Boffins build smallest drone to fly itself with AI

The Register

16 May 2018

Flying in dynamic, urban, highly-populated environments represents a challenge. We have managed to build a hand-sized drone that can fly autonomously and consumes only about 94 milliWatts of energy. Learn more about our Crazyflie 2.0 Nano Quadcopter in this Register article.. For details on the actual implementation see this arXiv paper. And no worries! We are not building the Skynet. Learn more on AI misconceptions in this article by Rodney Brooks from MIT.

AI Comes to Sensing Devices

EETimes

26 February 2018

EETImes published an article on GAP8, an IoT processor, built by GreenWaves Technologies, Grenoble, France, based on the RISC-V and PULP open-source projects. The processor is designed to perform image, sound and vibration AI analysis on battery-operated sensing devices. GAPUINO, an Arduino Uno compatible Master or Shield with a camera connector was rolled out in April, as well. Learn more about it here .

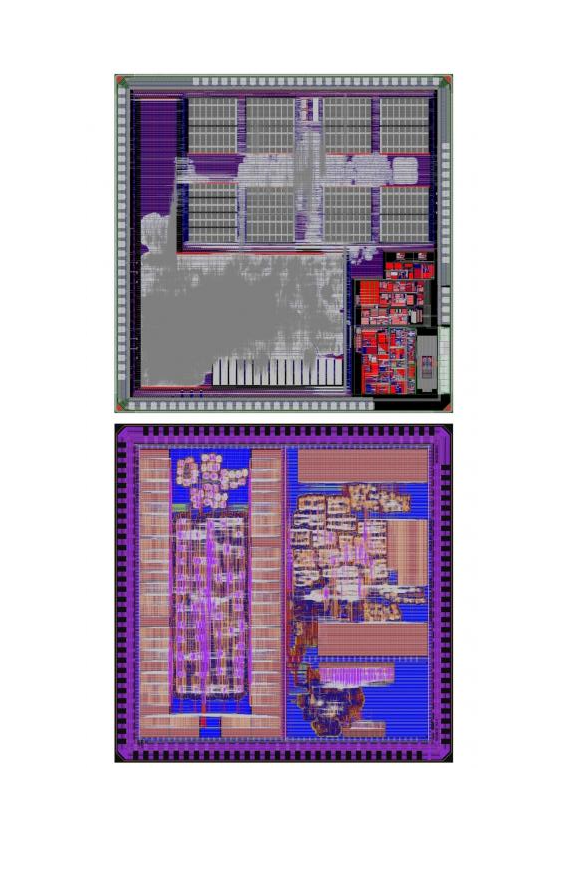

RISC-V-Prozessoren für Embedded Systems und Linux mit PULP

Heise Online

8 February 2018

Heise.de published an article about two of our recent designs, Mr. Wolf and Poseidon. The IoT processor Mr. Wolf contains eight 32bit RI5CY cores and an additional Zero-riscy core and our latest 22nm design Poseidon contains a 64bit Ariane processor. For more information about the implementation see this article or visit our chip gallery (Poseidon, Mr. Wolf).

RI5CY strategy

HiPEACinfo 52

October 2017

The HIPEAC newsletter, a quarterly publication on the latest activities of the European high-performance scene, published an announcement about a major release of our open-source (hardware and software) RISC-V based PULP platform. With two different cores, i.e. 4-stage RI5CY and a 2-stage Zero-riscy, you will now be able to select four different configurations for PULPino. Learn more about our RI5CY strategy on page 9 of HiPEACinfo 52.