Latest news

We have coorganised EFCL Winter School

February 12, 2026

We have coorganised EFCL Winter School on Open Source IC Design and ML acceleration for people interested in modern computer architectures, digital IC design, programming of heterogeneous systems and open source hardware. Four days of teaching activities were conducted in two parallel tracks, namely End-to-end open-source Digital IC Design and FPGA implementations of RISC-V based micro-controllers with accelerators. The event featured a TinyTapeout workshop, a series of Lectures on Analog Circuits for Non-Analog Designers and keynote talks from Luca Benini, Onur Mutlu, Ingrid Verbauwhede, Siyu Tang and Melika Payvand, as well. See the details of the event here.

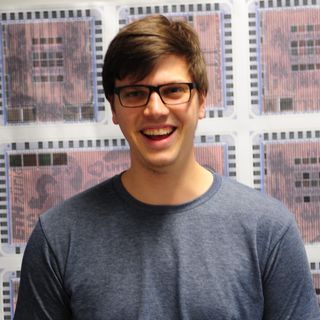

Best Student Poster award at HotChips 2025

August 27, 2025

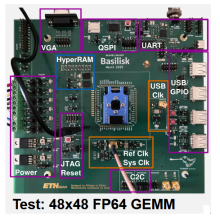

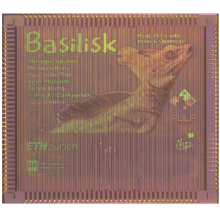

Great news from HotChips! Philippe just won The Best Student Poster award for our open-source IC design, Basilisk, the largest end-to-end open-source SoC to date. This is a 2.7 MGE design with a 64-bit Linux-capable RISCV core, a lightweight 124 MB/s DRAM controller, and extensive IO, including a USB 1.1 host, a video output, and a fully digital 62 Mb/s chip-to-chip link. Find the poster "34 mm² End-to-End Open-Source 64-bit Linux-Capable RISC-V SoC in 130nm BiCMOS" here.

Basilisk has been fully brought up

May 1, 2025

We have now fully brought up Basilisk, the first end-to-end open-source application-class SoC autonomously booting Linux designed using exclusively open-source tools (KiCad, Yosys, OpenROAD, KLayout) and open-source hardware designs targeting IHP's open 130nm node. The complete source code of the design is available under this link. The design has received generous support from Leibniz Institute for High Performance Microelectronics. Read more here.

Our Trikarenos was sent into orbit

March 15, 2025

Launched with the SpaceX transporter, our fault tolerant chip Trikarenos was sent into orbit on March 15, with ALICE by the Swiss Academic Space Initiative. Trikarenos by Michael Rogenmoser features triple redundancy, meaning it can continue functioning even if part of the chip fails. In space, where repairs are impossible, this is a crucial advantage. Trikarenos has such a high level of redundancy while maintaining extremely low power consumption, another essential characteristic for space applications. Read more here.

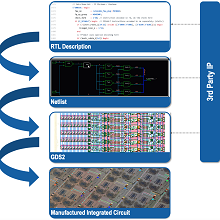

Our IC Design course is almost all open-source

February 20, 2025

At ETH Zurich we have a long tradition of offering a hands-on course for IC Design. Starting from 2025, we have migrated this course to use (mostly) open source EDA using the image from Harald Pretl, open source IP - our Croc and open source PDK from IHP. All material for the open tools are being added to our wiki. This is a work in progress, but we are confident that we will have most in place by the end of the semester and continue to improve it in the upcoming years.

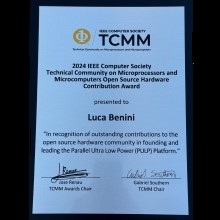

Luca receives the 2024 TCMM Open Source Hardware Contribution Award

August 28, 2024

Luca Benini received the 2024 TCMM Open Source Hardware Contribution Award in recognition of outstanding contributions to the open source hardware community in founding and leading the Parallel Ultra Low Power (PULP) Platform. The award was presented at Hot Chips 2024. Read the announcement here.

We have co-organized EFCL Summer School

June 8, 2024

We have co-organized EFCL Summer School on Open Source IC Design and Computer Architectures which took place 3 - 7 June 2024 in Zurich. The event was organised in three parallel hands-on tracks and one lecture track, namely Digital IC Design with Open Source EDA Tools, Customizing RISC-V based microcontrollers, Embedded AI for Biosignal Processing; and Computer Architecture and Memory Systems. Every day started with a keynote talk by a renowned scientist, among them Yale Patt, Andrew Kahng, Luca Benini, Onur Mutlu and Lana Josipovic. The summer school attracted more than 120 participants. See the EFCL website for details.

We open-sourced PULP-Detector

April 26, 2024

We open-sourced PULP-Detector, a nano-drone system that strives for maximizing the exploration of a room while performing visual object detection. The object detection CNN is based on the MobilenetV2-SSD network. The drone performs obstacle avoidance thanks to Time-of-flight sensors. The drone is completely autonomous -- no human operator, no ad-hoc external signals, and no remote laptop! See it on GitHub, Youtube and arXiv.

ISSCC 2023 Outstanding Forum Presenter Award

February 20, 2024

Congratulations to our team member Angelo Garofalo who won the ISSCC 2023 Outstanding Forum Presenter Award for his last year's contribution "Is an AI Accelerator All You Need? Overcoming Amdahl’s Law With Tightly-Coupled Specialized Accelerators. See the slides from his talk on our website.

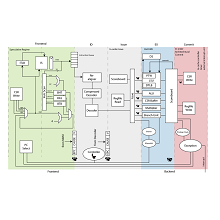

Our open-research heterogeneous platform Carfield released

January 31, 2024

We are delighted to release Carfield, our open-research heterogeneous platform for safety, resilient, and time-predictable systems. It now comes with an exhaustive documentation and an end-to-end getting started guide that will help you run tests and applications smoothly. See Carfield on GitHub. Learn more about it here.

PULP scoring at AMD Open Hardware 2023

September 04, 2023

Our HEROccamy team, represented by Cyril, Nils and Gianna, won in the PhD category of the AMD University Program Open Hardware 2023 competition. The annual design competion initiated by Xilinx gives university students the opportunity to showcase their technical and creative skills with adaptive compute technology.You can find the competition results here and our contribution titled "HerOccamy - A Fully RISC-V Heterogeneous SoC Research Platform" on Youtube.

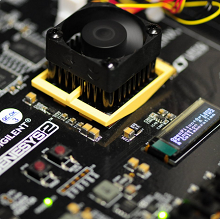

Occamy is back from assembly

August 18, 2023

Our 432-core Multi-TFLOPs RISC-V-Based 2.5D Chiplet System for Ultra-Efficient (Mini-)Floating-Point Computation just came back from assembly at Fraunhofer IZM. We are ready to test. The Occamy project started as a serendipitous outcome of the Manticore high-performance architecture concept and was made possible by the generous contribution and strong support of GlobalFoundries, Rambus, Micron, Synopsys and Avery. Read more about one of our most ambitious endeavours here.

Best paper award at ISVLSI2023

July 03, 2023

Our team received this year's ISVLSI best paper award for their work on a novel HW & SW stack for energy-efficient inference of mixed-precision QNNs. You can find "A 3 TOPS/W RISC-V Parallel Cluster for Inference of Fine-Grain Mixed-Precision Quantized Neural Networks" by Alessandro Nadalini, Georg Rutishauser, Alessio Burrello, Nazareno Bruschi and Angelo Garofalo on arXiv. We have likewise published the accompanying slides presented at ISVLSI in Iguazu.

We are celebrating 10 years of PULP

June 06, 2023

Did you know? PULP is celebrating its 10 year anniversary. To that end, our team got together at USI Lugano, West campus to take a look at what we accomplished and where we would like to be in ten year's time. Over the course of two days, our team members presented their work in the sections Microcontroller verticals, PULP Instances for High Performance, Acceleration and PULP SW environment. All of that was topped by an excursion to Lugano's Monte Bre, as well as dinner at Villa Ciani masterfully organised by our friend Francesco Regazzoni. You can find the slides from the event on a dedicated webpage.

PULP at DATE2023 in Antwerp

April 20, 2023

This year's Design, Automation and Test in Europe DATE took place in Antwerp. Ten PULP team members have showcased their work both during presentation and poster sesions. Starting from 10 Years of Open Source Hardware with PULP, we have presented our work on 5G-PUSCH, MemPool, TransLib, AXI-Pack, Occamy, HULK-V, as well as our research on CNN-based Object Detection on Nano-drones and On-board Low-Power Localization on Nano-UAVs. You can find all our presentations and posters here.

PULP at ISSCC2023

February 23, 2023

The PULP team had a strong representation at ISSCC 2023 that took place in San Francisco. Luca Benini gave a tutorial on Extending Processor Cores for Machine Learning, while Francesco Conti presented his work AI-IoT SoC Marsellus. Angelo Garofalo gave a talk on how to overcome Amdahl’s Law With Tightly-Coupled Specialized Accelerators. You can find Francesco's slides and Angelos's slides on our website.

GAP9 scoring first at MLCommons

November 10, 2022

MLCommons, the foundation which established industry-standard metrics to measure machine learning performance, published the data from its benchmark suite v1.0 featuring GAP9 by Greenwaves Technologies with PULP inside at the first position. You can find the scenarios, metrics and results of the benchmark here.

PULP team first in the Nanocopter AI challenge

September 19, 2022

Our team has won the 1st prize in the Nanocopter AI challenge at IMAV2022 TU Delft. as well as a special award in the Greenhouse challenge for being the only nano-drone. PULP team did a 110m-flight in 5' with 0 crashes - fully autonomous nano-drone and dynamic obstacles in the flight arena. Congratulations to our representative Lorenzo Lamberti! Check out the videos 1,2 and 3 from the event.

ControlPULP receives open source award at Samos XXII

July 7, 2022

The PULP team participated at this year's International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation SAMOS XXII in the sunny Greece. Here Sergio Mazzola presented his work on Lightweight DVFS-aware Counter-based Power Modeling, while Davide Nadalini introduced PULP-TrainLib. Additionally, Alessandro Ottaviano's and Robert Balas's paper "ControlPULP: A RISC-V Power Controller for HPC Processors with Parallel Control-Law Computation Acceleration" received the Samos open source HW/SW award. Congratulations!

PULP participates at RISC-V Spring Week in Paris

May 9, 2022

This year's RISC-V Spring Week took place in Paris and we are delighted that so many members of our team could partake in this successful event. Andrea and Alessandro presented their RISC-V based Power Management Unit for an HPC processor, while Matheus demonstrated his work on RISC-V based Stencil Tensor Accelerator of EPI. Similarly, Andrea, Gianluca, Sergio, Alaa, Lukas, Gianmarco and Alessandro presented their RISC-V related work in the poster session. You can find many of their posters here.

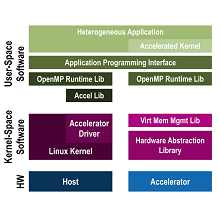

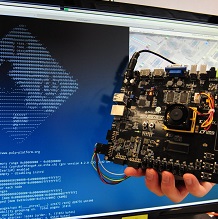

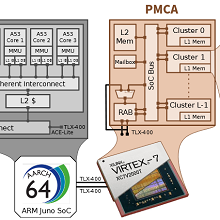

Our team has successfully released HEROv2

January 14, 2022

We have released HEROv2, an update to our FPGA-based full-stack open-source research platform for heterogeneous computing. With HEROv2 you get an FPGA-based 64-bit ARMv8 + 32-bit RISC-V heterogeneous computer, full software stack from API over runtime libs and OS to low-level routines and a heterogeneous compiler for seamless offloading and data sharing. Learn more in this paper and check it out on GitHub.

PULP joined EuPilot

December 1, 2021

PULP team joined a brand new project around the European Processor Initiative. The European Pilot will deliver the first All-European open source and open standard based software and hardware integrated HPC system by creating an autonomous set of accelerators designed, implemented, manufactured, and deployed in Europe. The accelerators will be manufactured in the new European Global Foundries 12 nm advanced silicon technology. Learn more on the project page.

EPI successfully ran initial tests on EPAC1.0

September 22, 2021

The European Processor Initiative (EPI), a project with 28 partners from 10 European countries, announced that the initial tests of their EPAC1.0 RISC-V Test Chip samples were successful. The test chip was released for fabrication in GF 22FDX in June 2021. PULP contributed to the EPI effort with the Stencil and Tensor accelerator (STX). Read more about the project and its aims on EPI's website.

Photo Courtesy European Processor Initiative (2021)

PULP participates at ACACES Summer School 2021

September 12, 2021

The 17th International Summer School on Advanced Computer Architecture and Compilation for High-performance Embedded Systems organised by HIPEAC in Fiuggi, Italy presented a unique opportunity for PULP members to advance their knowledge, as well as to present their work. Luca Benini and Davide Rossi gave a course on Working with RISC-V: from open ISA to open Architecture to open Hardware. Our Phd Students Matteo, Robert, Moritz, Nils and Cioflan participated to the ACACES courses while exploring the picturesque Fiuggi.

PULP and Bitcraze organized an AI-deck workshop

April 16, 2021

PULP in collaboration with Bitcraze organized an afternoon workshop on AIdeck featuring the GAP8 IoT application processor from GreenWaves Technologies. Lorenzo, Hanna, Vlad, Manuele and Daniele gave an overview of PULP, GAP8 and AI-deck. This was followed by a hands-on session which included JTAG programming, image manipulation, video streaming and firmware integration. You can find the recordings and the accompanying slides here.

PULP launches a dedicated training page

March 11, 2021

We have launched a page specifically dedicated to PULP's training materials. You can find there more than 13 hours of videos, slides and even a VM setup. Check out "Understanding and working with PULP" by Davide Schiavone, take the "GVSoC / Dory Tutorial" with Nazareno Bruschi and Alessio Burello or "A Deep Dive into HW/SW Development with PULP" by Robert Balas and Manuel Eggimann. Learn everything about PULP on our training page.

PULP at DATE 2021

February 5, 2021

This year's conference Design, Automation and Test in Europe happened to be virtual, but that did not prevent us from making a large-scale contribution. Seven of our Ph.D. students presented their work in different tracks. Our paper "Microarchitectural Timing Channels and their Prevention on an Open-Source 64-bit RISC-V Core" by Nils Wistoff et al. received the Best Paper Award in the T Track of the conference. Additionally, Luca presented his thoughts on Moore's Law and job opportunities in IC design. You can find all of our conference slides here.

HIPEAC Vision and Open source hardware

January 19, 2021

The new edition of HIPEAC Vision 2021 features an article titled "Open source hardware is here to stay" by Frank Gurkaynak. In it, Frank highlights the differences between open source hardware and software development and traces its development over time. Furthermore, he advocates that Open source hardware be the key ingredient to allow agile co-operation of partners both in academia and industry, essential for modern integrated circuit design. You can find the article on pages 192-197 of the HIPEAC Vision 2021.

Europe, PULP and open hardware efforts

December 9, 2020

A very recent presentation by Luca Benini to the European Union explains the situation and requirements of open hardware scene in Europe. It presents the increasingly important role of RISC-V and the success of the PULP platform. Further, it mentions open collaboration schemes that lead to successful product development, such as GAP8, as well as the transition from academic open source to industrial open source as exemplified e.g. by the OpenHW group. Last, the presentation highlights the importance of public EU funding to facilitate prototyping and to nurture the open hardware ecosystem. You can find the presentation here.

PULP participated at the RISC-V Summit with four talks

December 9, 2020

This year's RISC-V Summit took place online but that didn't prevent us from contributing to a marked extent. We have had two contributions by our two new PhD students, Luca Bertaccini with A Tiny RISC-V Floating-Point Unit and Nils Wistoff with Time Protection: Preventing Microarchitectural Timing Channels on RISC-V. And of course our seasoned team members presented, as well. Francesco Conti with An Open-Source Flow for DNNs on Ultra-Low-Power RISC-V Cores and Florian Zaruba with CORE-V MCU SoC, Open Source, 22nm Embedded MCU with eFPGA. You can find all of their talks here.

Two awards for the PULP team

November 20, 2020

We are celebrating and not just once! We have been fortunate to receive two awards. Luca Benini has been awarded A. Richard Newton Technical Impact Award in Electronic Design Automation for the paper Networks on chips: a new SoC paradigm (2002). Michael Gautschi and colleagues received the 2020 IEEE Transactions on Very large Scale Integrated Systems (TVLSI) Best Paper Award for their paper Near-Threshold RISC-V Core With DSP Extensions for Scalable IoT Endpoint Devices (2017)

AntMicro published the results of their CPU tests

September 22, 2020

AntMicro published the results of their automatic CPU testing with Embench-LiteX tester. You can study how our RI5CY (CV32E40P) and other cores fare when compared to ARM Cortex M4 for 19 different algorithms here. Where relative results are concerned, higher values are better. For absolute results in [ms] lower values are better.

PULP Hackathon 2020

July 31, 2020

After a long period of virtual events, we have organized our very first internal hackathon. Thanks to the initiative of our colleague Xiaying, this turned out to be a very successful event. The goal of the event was to optimize the functions in the PULP DSP library. Participants ranged from PULP newbies who have never run any code on PULP platforms to PULP pros who are experts in writing optimized PULP codes. Read Xiaying's report here.

Ariane now with the OpenHW Group

June 16, 2020

Just like our 32-bit cores RI5CY (CV32E40P) and Zero-riscy (Ibex), also our 64-bit Ariane core has found a new home. Ariane has been taken over by the OpenHW Group under the name CVA6 and will be taken care of it as part of the Core-V project. You can find the repository here.

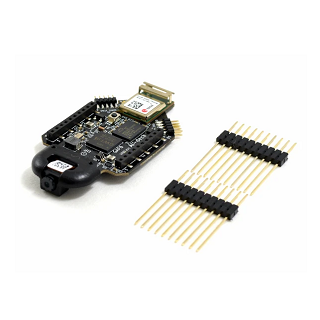

AI-deck is available in early access

June 8, 2020

AI-deck, a collaborative product of BitCraze, GreenWaves Technologies and ETH Zurich has been just released. The deck is capable of hosting artificial intelligence-based workloads and thereby enabling super-edge computing on Crazyflie thanks to the GAP8 processor. The ESP32 adds WiFi connectivity with the possibility to stream images as well as handling control. You can find it in the online store of Bitcraze. Learn more here..

PULP at HiPEAC Bologna and The European Green Deal

January 24, 2020

The annual HiPEAC conference, Bologna 2020 just successfully concluded and as the venue is the second home of PULP, our team couldn't miss the opportunity to attend and present their work. You can find the presentations of Luca, Davide and Frank here. Additionally, Frank co-organized the Eurolab4HPC Industrial session on Open HW which turned out to be a great success. As part of the conference, the EC's Sandro D'Elia announced trillion-Euro Green Deal to make Europe the world's first climate neutral continent by 2050 and as PULP and energy efficiency go hand in hand, we will do our best to contribute. Read more in EETimes.

PULP inside OpenHW Group's heterogeneous multi-core processor

December 11, 2019

OpenHW Group is going to tape out a heterogeneous multi-core processor based on the NXP iMX platform incorporating open source CORE-V components. The 64-bit CV64A core in the CORE-V Chassis is based on the RV64GC RISC-V core IP, originally developed as part of PULP. Optimized for performance, the CV64A core will be capable of clock frequencies of 1.5GHz. Learn more here.

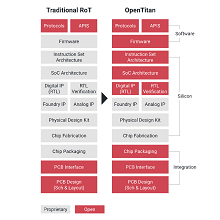

Google releases OpenTitan

November 5, 2019

Google's OpenTitan, an open source silicon root of trust project, with our Ibex as a key element, has just been announced. Silicon RoT can help ensure that the hardware infrastructure and the software that runs on it remain in their intended, trustworthy state by verifying that the critical system components boot securely using authorized and verifiable code. Several organisations are already participating including ETH Zurich, Google, G+D Mobile Security, Nuvoton, Western Digital and lowRISC. Learn more here and on Google's blog..

Our team released PULP-NN

July 29, 2019

Angelo Garofalo, Manuele Rusci, Francesco Conti and Davide Rossi from our team have released PULP-NN, a multicore computing library to run Quantized Neural Networks on our PULP platform or any of its multi-core (cluster) embodiments and is much like the CMSIS-NN (ARM) data flow and data layout. The first release supports 8-bit weights and activations, and further updates will also include support for sub-byte data operands, down to 1-bit. Learn more here.

RISC-V Workshop and WOSH in Zurich have been a success

June 20, 2019

The RISC-V Workshop and the Week of Open Source hardware at ETH Zurich are now over and we are very proud to have hosted and co-organized this event, an acknowledgement of the growing importance of the RISC-V architecture. During the four days of the workshop and the WOSH tutorials we had the opportunity to learn from top class speakers, meet interesting people, as well as enjoy the views of Zurich. It's been a great pleasure to meet you all. You can find the photos from the event here.

OpenHW Group has been created and PULP is in

June 7, 2019

A new not-for-profit global organization has been founded to boost the adoption of open-source processors by providing a platform for collaboration and offering open-source IP for processor cores. Headed by Founder and CEO, Rick O'Connor, the OpenHW Group has already recruited 13 sponsor organizations, among them Alibaba, Bluespec, CMC Microsystems, Embecosm, ETH Zurich, GreenWaves, Imperas, Metrics, Mythic AI, NXP, Onespin, Silicon Labs and Thales. We are extremely proud to contribute the cores from our PULP Platform into the OpenHW Group family of Core-V cores. Learn more about the OpenHW Group.

lowRISC expands and appoints ETH Zurich to its Board of Directors

May 16, 2019

Prof. Luca Benini (PULP, ETH Zurich) together with Dominic Rizzo and Ron Minnich (Google) have joined the Board of Directors of lowRISC. This is in line with the aim of the organisation to lower the barriers to producing custom silicon, enabling research and FPGA experimentation, and establishing an ecosystem around open silicon designs. PULP is contributing its Zero-riscy processor core which will be further developed under the name 'Ibex'. Read more here.

Zero-riscy now at LowRISC as Ibex

May 7, 2019

Problem finding our Zero-riscy core? It has a new home at LowRISC, which have promised to take good care of it. To mark this change we have renamed the core Ibex (Mountain Goat). The repository https://github.com/pulp-platform/zero-riscy with all its comments and change history now resides under https://github.com/lowRISC/ibex and will continue to remain compatible to our project.

PULP has a Youtube channel

April, 2019

You can now watch PULP related projects and news on the Youtube channel that was started by Daniele Palossi from our team. Check out our first videos on the autonomous AI PULP Dro-Net and BioWolf. We would like to thank all the early subscribers - your support made it possible to reach the required mark for our own URL in no time.

PULP and the RISC-V tutorial at HIPEAC19

January 24, 2019

Andreas, Fabian, Michael, Frank and Alex the Bear from the PULP team have participated at HIPEAC19 in Valencia. During the first day of the event, they have given a RISC-V tutorial that included presentations, as well as hands-on related to PULP SDK, the Heteregeneous Research Platform Hero, PowerPULP and OpenPiton+Ariane. You can find the slides here. We would like to thank all the participants that attended the tutorial. The PULP team has also enjoyed the hospitality of the HIPEAC organising team, especially the walking dinner at the City of Arts and Sciences designed by Calatrava.

VEGABoard - New development board with PULP inside

December 3, 2018

If you were looking for a complete microcontroller development system based on PULP, now you have a new option. Check out the RV32M1VEGA development board by open-isa. VEGABoard is an evaluation board supporting RISC-V cores based RV32M1Wireless Microcontrollers. It integrates a radio tranceiver, ARM Cortex M4 CPU, ARM Cortex M0 CPU and our RI5CY MCU and Zero-Riscy MCU into a single unit. Learn more about VEGABoard's parameters from the documentation.

Announcing OpenPiton with Ariane

November 29, 2018

The Princeton Parallel Group led by David Wentzlaff, and the Digital Circuits and Systems Group of ETH Zurich led by Luca Benini have joined forces to bring you the OpenPiton open-source research processor platform with first-class support for 64-bit Ariane RISC-V cores. The latest update of the open-source Ariane processor, (Ariane IV) now supports the P-Mesh cache system from OpenPiton, and with today's OpenPiton release 10, we have our first working system.

The brand new Ariane IV launched

November 29, 2018

We are happy to announce Ariane IV. Besides many small performance improvements, bug fixes and enhancements, we now support booting an upstream RISC-V Linux on the Genesys2 FPGA board by Digilent. Check the following link to access pre-built bitfiles and SD images or have a look at the build flow on GitHub.

Francesco and Davide won The Best Paper Award at CODES+ISSS 2018

October 3, 2018

Congratulations to Francesco Conti and Davide Schiavone who won The Best Paper Award at CODES+ISSS 2018, Torino for their paper on XNOR Neural Engine: a Hardware Accelerator IP for 21.6 fJ/op Binary Neural Network Inference. You can find their paper on arXiv.

PULP participated at ORConf 2018

September 23, 2018

Davide Rossi and Frank Gurkaynak participated at ORConf 2018 in Gdansk, Poland organized by the FOSSi Foundation. Davide presented PULP Project updates, while Frank discussed the challenges of open-source hardware. Frank also represented PULP in the open-source silicon panel. The PULP team enjoyed interesting discussions on open-source topics in a relaxed atmosphere, as well as tasty Polish cuisine.

HERO has been just released

September 17, 2018

HERO is our open-source, FPGA-based heterogeneous SoC research platform that combines a fully modifiable RISC-V manycore accelerator with an ARM Cortex-A host processor. In addition to a silicon-proven RISC-V manycore accelerator, HERO includes a heterogeneous software stack that supports OpenMP 4.5 and Shared Virtual Memory for transparent accelerator programming; a cycle-accurate, non-interfering event tracing infrastructure complemented by a flexible event analysis and profiling framework and an automated implementation and validation solution that enables efficient research and development on all software and hardware layers. Learn more.

Confirmed: RISC-V workshop at ETH Zurich

June 11, 2018

Save the Dates! The PULP team will be organizing the next RISC-V workshop. The event will take place at ETH Zurich, Switzerland, 11-13 June 2019. We will let you know more, as soon as we work out the details.

QuickLogic on board with PULP

August 8, 2018

We are happy to announce that QuickLogic has started collaboration with ETH Zurich to integrate QuickLogic's ArcticPro embedded FPGA (eFPGA) technology into PULP platform. PULP will develop an SoC integrating RISC-V cores and eFPGA technology, enabling users to offload critical functions from the processors and implement them in eFPGA fabric. The fully integrated system with eFPGA is expected to be available Q1' 2019. Learn more...

The PULP team has a new member

July 26, 2018

We would like to introduce to you our new colleague Moritz Schneider who will soon start working on security extensions on PULP systems at IIS ETH Zurich. We hope he will like it with us.

The PULP team attended the NiPS Summer School

July 17 - 20, 2018

The PULP team participated in The Noise in Physical System Summer School in Perugia devoted to physical foundations and practical applications of energy transformations at micro and nanoscales. Davide, Andrea, Giuseppe, Fabian, Stefan, and Frank from our team also contributed to the great variety of interesting talks. You can find their talks here. Additionally, the PULP team has enjoyed great food, the Umbria jazz festival, as well as the trip to Lake Trasimeno.