Platform Overview

HERO consists of many different hard- and software components.

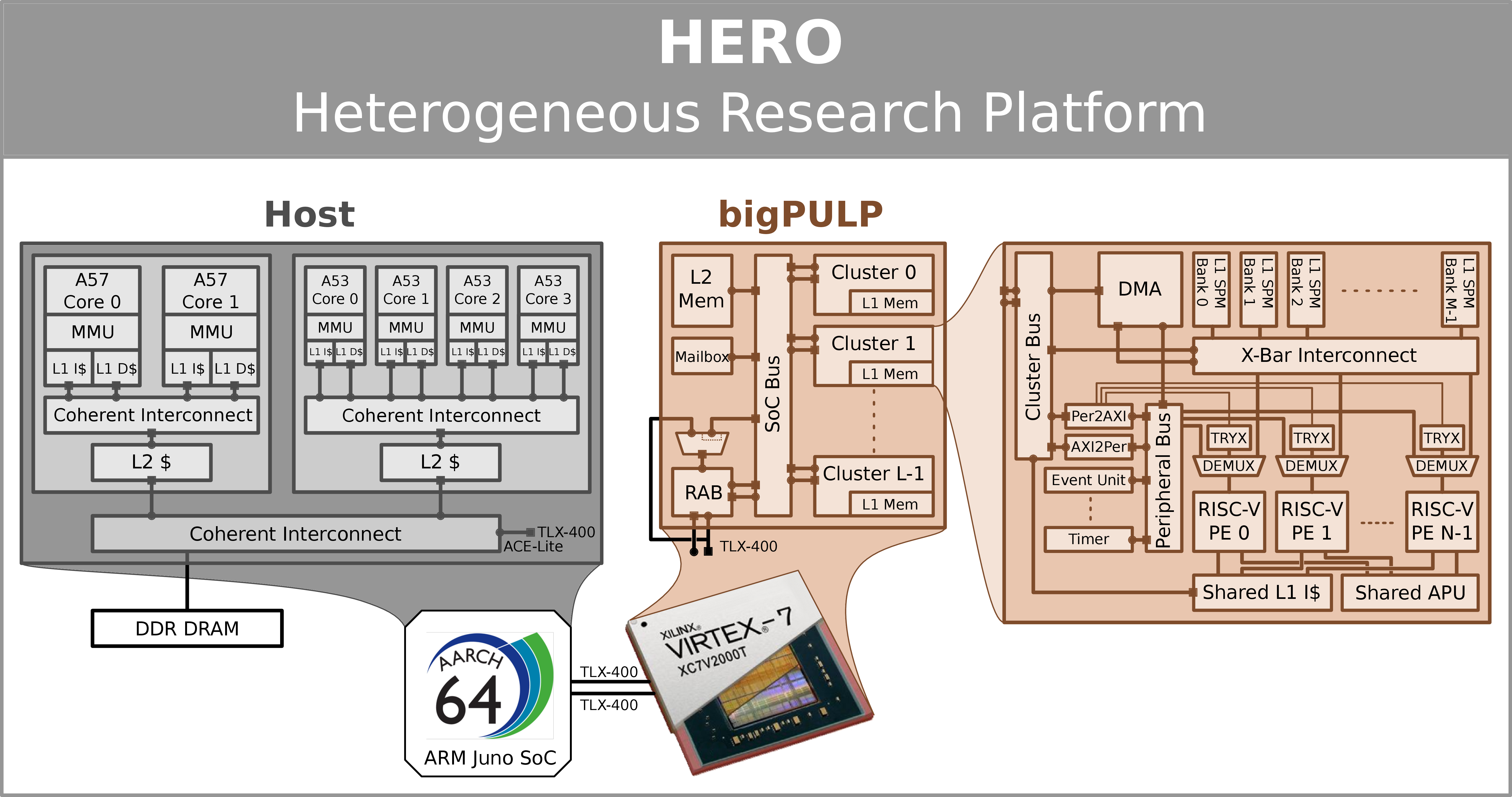

On the hardware side, HERO uses an ARM Cortex-A host processor combined with a RISC-V programmable manycore accelerator (PMCA) implemented on FPGA. As PMCA, HERO uses bigPULP, i.e., the big brother of the open-source, multi-core, Parallel Ultra-Low Power (PULP) computing platform jointly developed by ETH Zurich and the University of Bologna. BigPULP is based on the same cluster architecture and source code. Depending on the target FPGA, bigPULP uses one or multiple PULP clusters that share an L2 instruction and data memory, a global interconnect, synchronization infrastructure, as well as the Remap Address Block (RAB) - a software-managed I/O memory management unit - which allows accelerator to coherently access the platform’s main memory including support for shared virtual memory (SVM). How to generate the FPGA bitstream for HERO containing bigPULP is explained here.

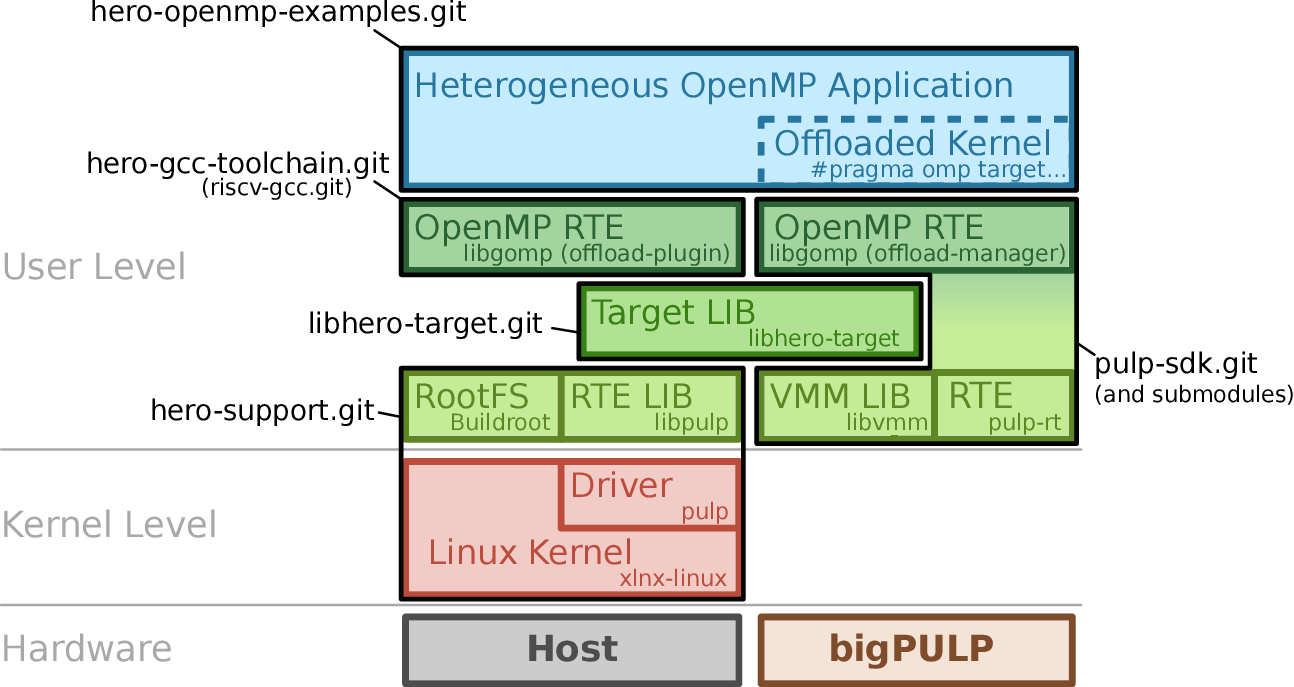

On the software side, HERO combines two different open-source software stacks. Both comprise various modules and are contained in the HERO SDK.

The programmer writes a single application source file for the host and uses OpenMP directives for parallelization and accelerator offloading. The host-side OpenMP runtime together with the accelerator plugin takes care of the actual offloading of the target section to the accelerator. Lower-level API calls are resolved to the corresponding, device-specific implementation by the target library. The accelerator uses the PULP Software Development Kit (SDK), which also provides accelerator-specific libraries such as the Virtual Memory Management (VMM) library and the accelerator-side OpenMP runtime. The host-side HERO software stack is completed by a user-space runtime library and kernel-level device driver, which take care of system-level tasks such as booting and synchronizing with the accelerator, and allowing the the accelerator manage the shared virtual memory (SVM) subsystem. The host itself runs a full-stack Linux. Depending on the selected FPGA board/host CPU, a different version is used. How to generate and customize the bootloaders, Linux kernel and root filesystem for the host is explained here.